52

CHAPTER 2 CPU

2.11 Precautions for Use of "DIV A, Ri" and "DIVW A, RWi"

Instructions

Set "00

H

" in the bank register before using the "DIV A, Ri" and "DIVW A, RWi"

instructions.

■ Precautions for Use of "DIV A, Ri" and "DIVW A, RWi" Instructions

If the value of the bank registers (DTB, ADB, USB, and SSB) is "00

H

", the remainder after division is

stored in the register of the instruction operands. Otherwise, the upper eight bits is specified by the bank

register corresponding to the register of the instruction operand, and the lower 16 bits is the same as the

address of the register of the instruction operand. The remainder is stored in the bank register specified by

the upper eight bits.

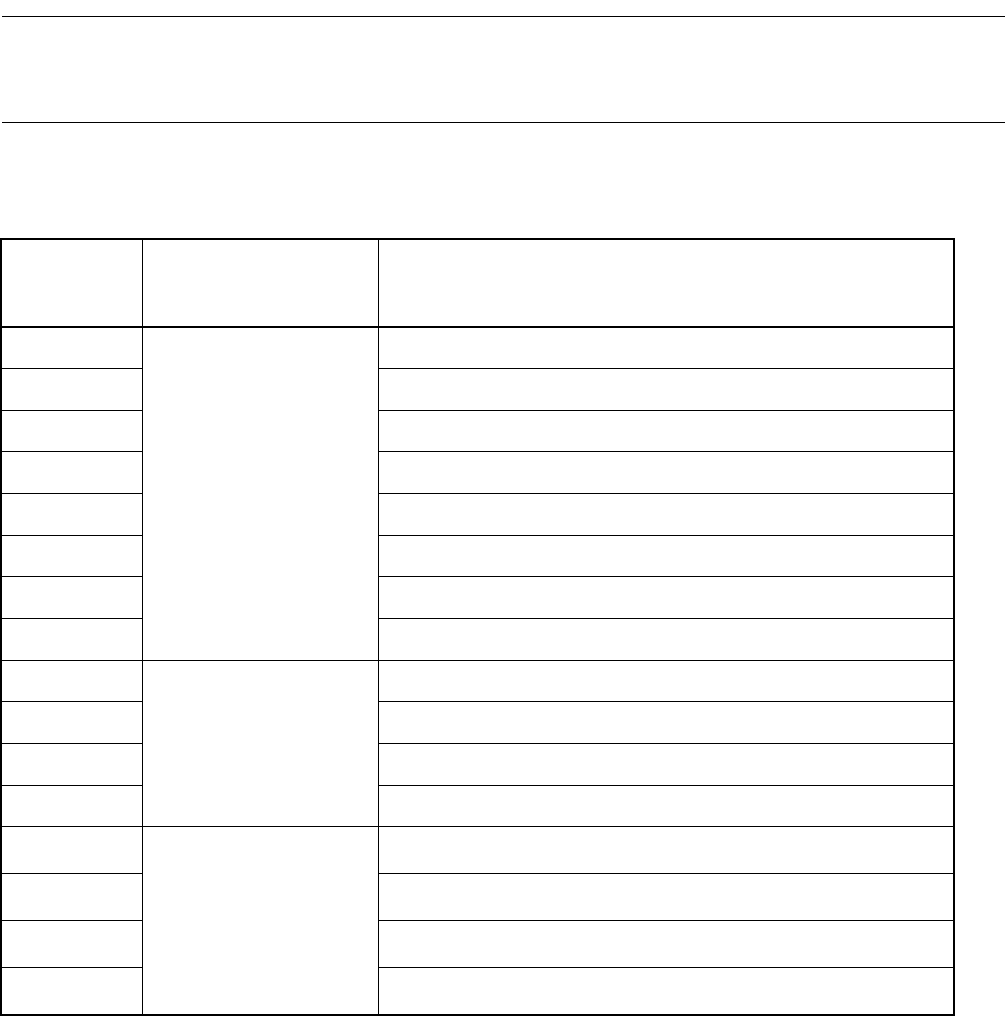

Table 2.11-1 Precautions for Use of "DIVA,Ri" and "DIVWA,RWi" Instructions (i=0 to 7)

Instruction

Bank register name affected

by the execution of the

instructions listed on the left

Address that stores the remainder

DIVA,R0

DTB

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+8

H

Lower 16 bits)

DIVA,R1

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+9

H

Lower 16 bits)

DIVA,R4

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+C

H

Lower 16 bits)

DIVA,R5

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+D

H

Lower 16 bits)

DIVWA,RW0

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+0

H

Lower 16 bits)

DIVWA,RW1

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+2

H

Lower 16 bits)

DIVWA,RW4

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+8

H

Lower 16 bits)

DIVWA,RW5

(DTB: Upper 8 bits)+(0180

H

+RP × 10

H

+A

H

Lower 16 bits)

DIVA,R2

ADB

(ADB: Upper 8 bits)+(0180

H

+RP × 10

H

+A

H

Lower 16 bits)

DIVA,R6

(ADB: Upper 8 bits)+(0180

H

+RP × 10

H

+E

H

Lower 16 bits)

DIVWA,RW2

(ADB: Upper 8 bits)+(0180

H

+RP × 10

H

+4

H

Lower 16 bits)

DIVWA,RW6

(ADB: Upper 8 bits)+(0180

H

+RP × 10

H

+E

H

Lower 16 bits)

DIVA,R3

USB, SSB

*1

(USB

*2

: Upper 8 bits)+(0180

H

+RP × 10

H

+B

H

Lower 16 bits)

DIVA,R7

(USB

*2

: Upper 8 bits)+(0180

H

+RP × 10

H

+F

H

Lower 16 bits)

DIVWA,RW3

(USB

*2

: Upper 8 bits)+(0180

H

+RP × 10

H

+6

H

Lower 16 bits)

DIVWA,RW7

(USB

*2

: Upper 8 bits)+(0180

H

+RP × 10

H

+E

H

Lower 16 bits)

*1: Depends on the S bit of the CCR register

*2: In the event that S bit of the CCR register is 0