164

CHAPTER 9 MEMORY ACCESS MODES

9.1.2 Mode Data

Mode data is stored at FFFFDF

H

of main memory and used for controlling the CPU

operation. This data is fetched during a reset sequence and stored in the mode register

inside the device. The mode register value can be changed only by a reset sequence.

The setting of this register is valid after the reset sequence.

Always set the reserved bits to "0".

■ Mode Data

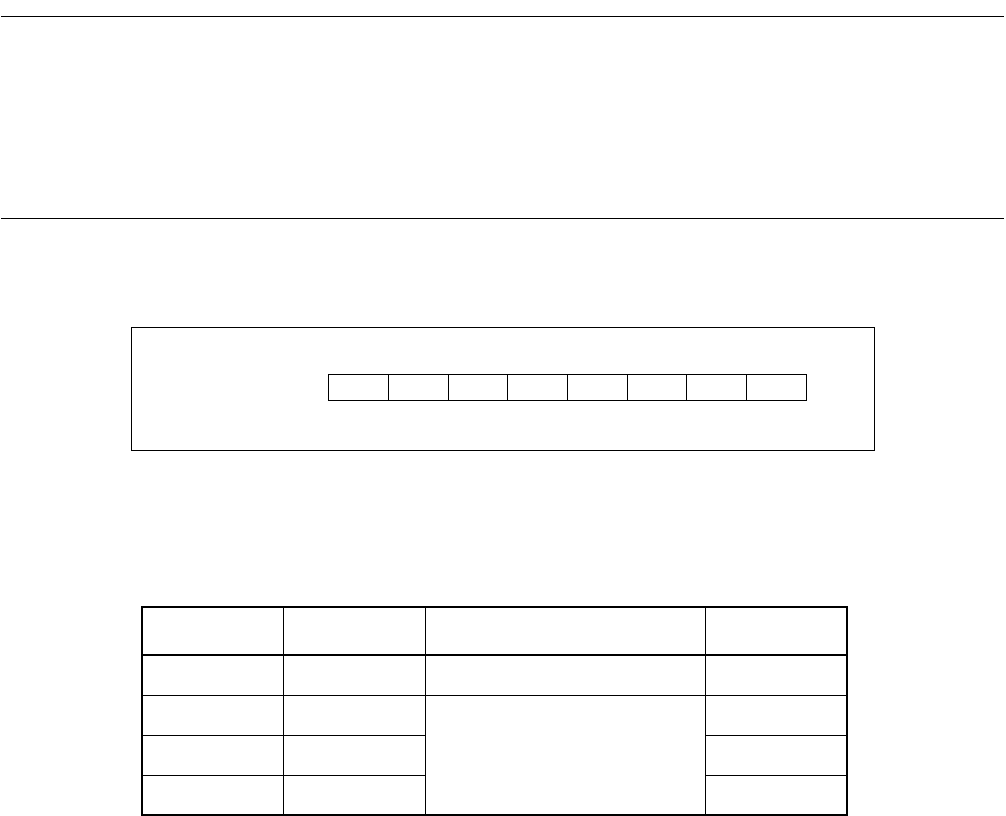

Figure 9.1-1 Mode Data Configuration

[bit7 and bit6] M1, M0 (bus mode setting bits)

The M1 and M0 bits are used to specify the operation mode after the reset sequence is completed. Table

9.1-3 shows the relationship between the M1 and M0 bits and the functions.

76543210

Address: FFFFDF

H

M1 M0

Reserved Reserved Reserved Reserved Reserved Reserved

Table 9.1-3 Function of M1, M0 (bus mode setting bit)

M1 M0 Function Remarks

0 0 Single-chip mode

0 1 Setting disabled

1 0

1 1