71

CHAPTER 3 INTERRUPTS

3.5.3 Multiple interrupts

As a special case, no hardware interrupt request can be accepted while data is being

written to the I/O area. This is intended to prevent the CPU from operating falsely

because of an interrupt request issued while an interrupt control register for a resource

is being updated.

If an interrupt occurs during interrupt processing, a higher-level interrupt is processed

first.

■ Multiple Interrupts

The F

2

MC-16LX CPU supports multiple interrupts. If an interrupt of a higher level occurs while another

interrupt is being processed, control is transferred to the high-level interrupt after the currently executing

instruction is completed. After processing of the high-level interrupt is completed, the original interrupt

processing is resumed. An interrupt of the same or lower level may be generated while another interrupt is

being processed. If this happens, the new interrupt request is suspended until the current interrupt

processing is completed, unless the ILM value or I flag is changed by an instruction. The extended

intelligent I/O service cannot be activated from multiple sources; while an extended intelligent I/O service

is being processed, all other interrupt requests or extended intelligent I/O service requests are suspended.

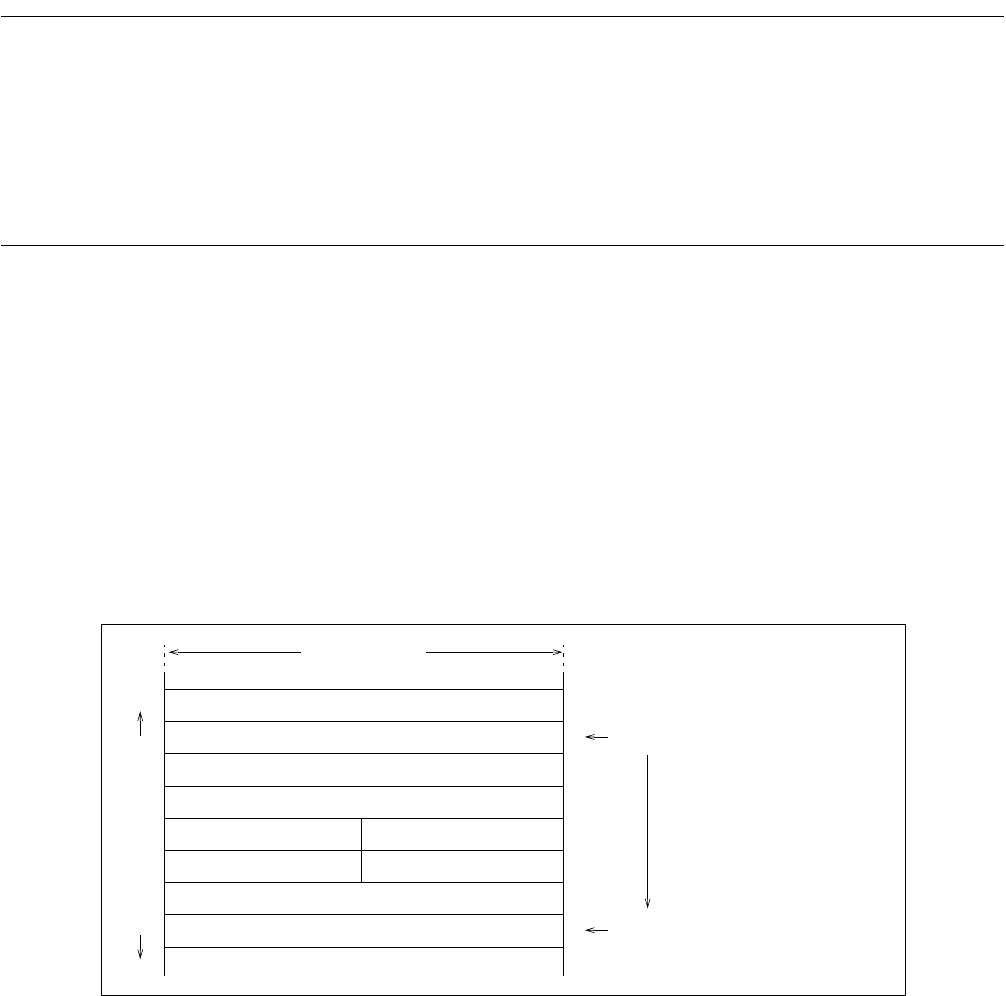

Figure 3.5-2 shows the order of the registers saved in the stack.

Figure 3.5-2 Registers Saved in Stack

"H"

"L"

MSB

LSB

AH

AL

PC

PS

ADB

PCBDPB

DPR

Word (16 bits)

SSP (SSP value before interrupt)

SSP (SSP value after interrupt)