185

CHAPTER 11 TIMEBASE TIMER

11.3.1 Timebase timer control register (TBTC)

The timebase timer control register (TBTC) provides the following settings:

• Selecting the interval time of the timebase timer

• Clearing the counter value of the timebase timer

• Enabling or disabling the interrupt request when an overflow occurs

• Checking and clearing the state of the interrupt request flag when an overflow occurs

■ Timebase Timer Control Register (TBTC)

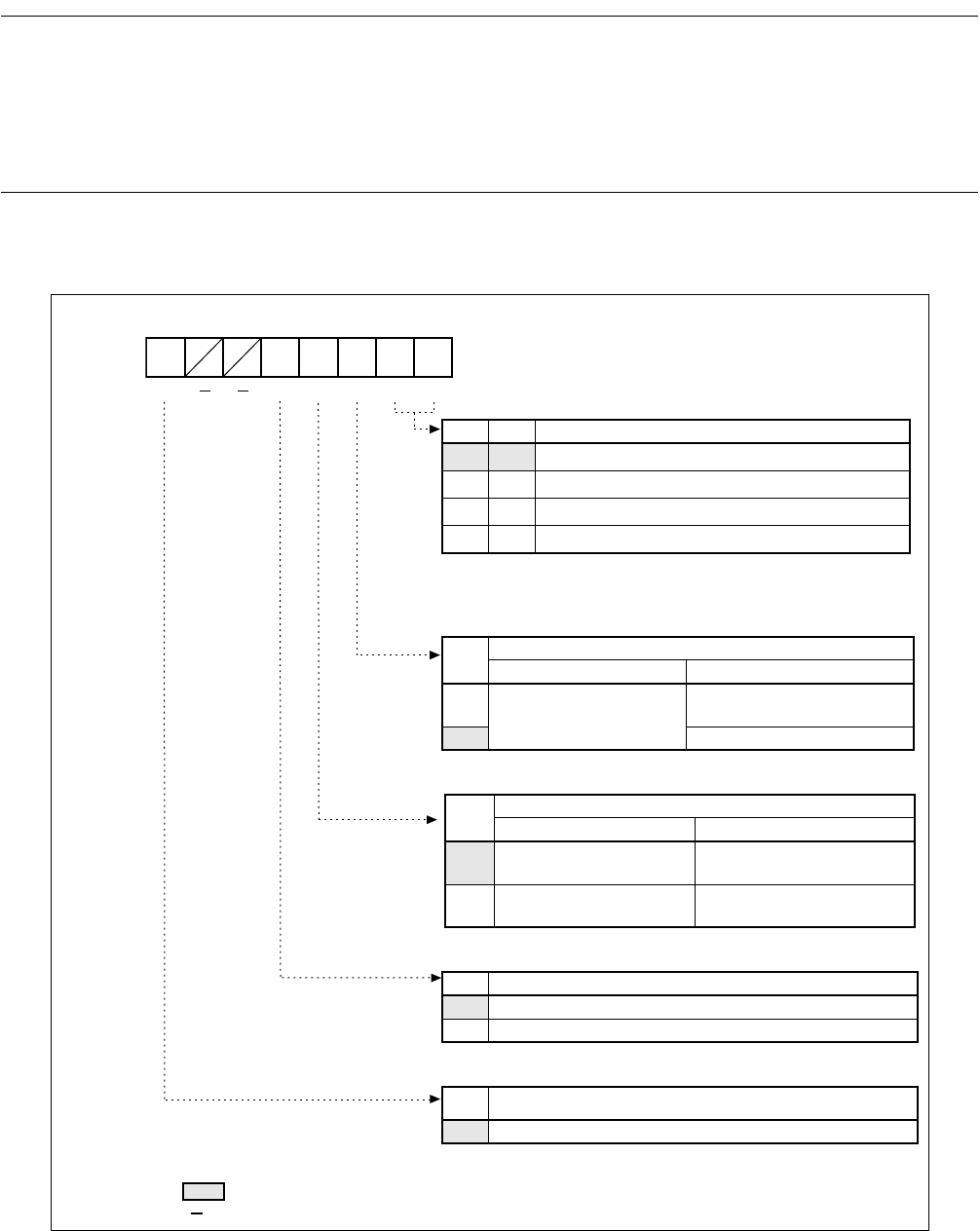

Figure 11.3-2 Timebase Timer Control Register (TBTC)

1XX00100B

1213 11 10 9

14

R/W R/W R/W W R/W R/W

8

15

R/W

W

X

TBIE TBOF TBR TBC1 TBC0

Re-

served

HCLK: Oscillation clock

The parenthesized values are provided when the oscillation clock

operates at 4 MHz.

bit9 bit8

TBC1 TBC0 Interval time select bit

0 0

2

12

/HCLK (approx. 1.0 ms)

01

2

14

/HCLK (approx. 4.1 ms)

10

2

16

/HCLK (approx. 16.4 ms)

11

2

19

/HCLK (approx. 131.1 ms)

bit10

TBR Timebase timer counter clear bit

Read Write

0

"1" is always read.

Clear timebase timer counter.

Clear TBOF bit.

1No effect

bit11

TBOF Overflow interrupt request flag bit

Read Write

0 Without overflow of selected

count bit

Being clear.

1 With overflow of selected

count bit

No effect

bit12

TBIE Overflow interrupt enable bit

0 Disabling of overflow interrupt request

1 Enabling of overflow interrupt request

bit15

Re-

served

Reserved bit

1 "1" is always set.

Reset value

: Read/write

: Write only

: Indeterminate

: Reset value

: Undefined

Address

0000A9

H