513

CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION

22.3.2 Detect Address Setting Registers (PADR0 to PADR5)

The value of an address to be detected is set in the detect address setting registers.

When the address of the instruction processed by the program matches the address set

in the detect address setting registers, the next instruction is forcibly replaced by the

INT9 instruction, and the interrupt processing program is executed.

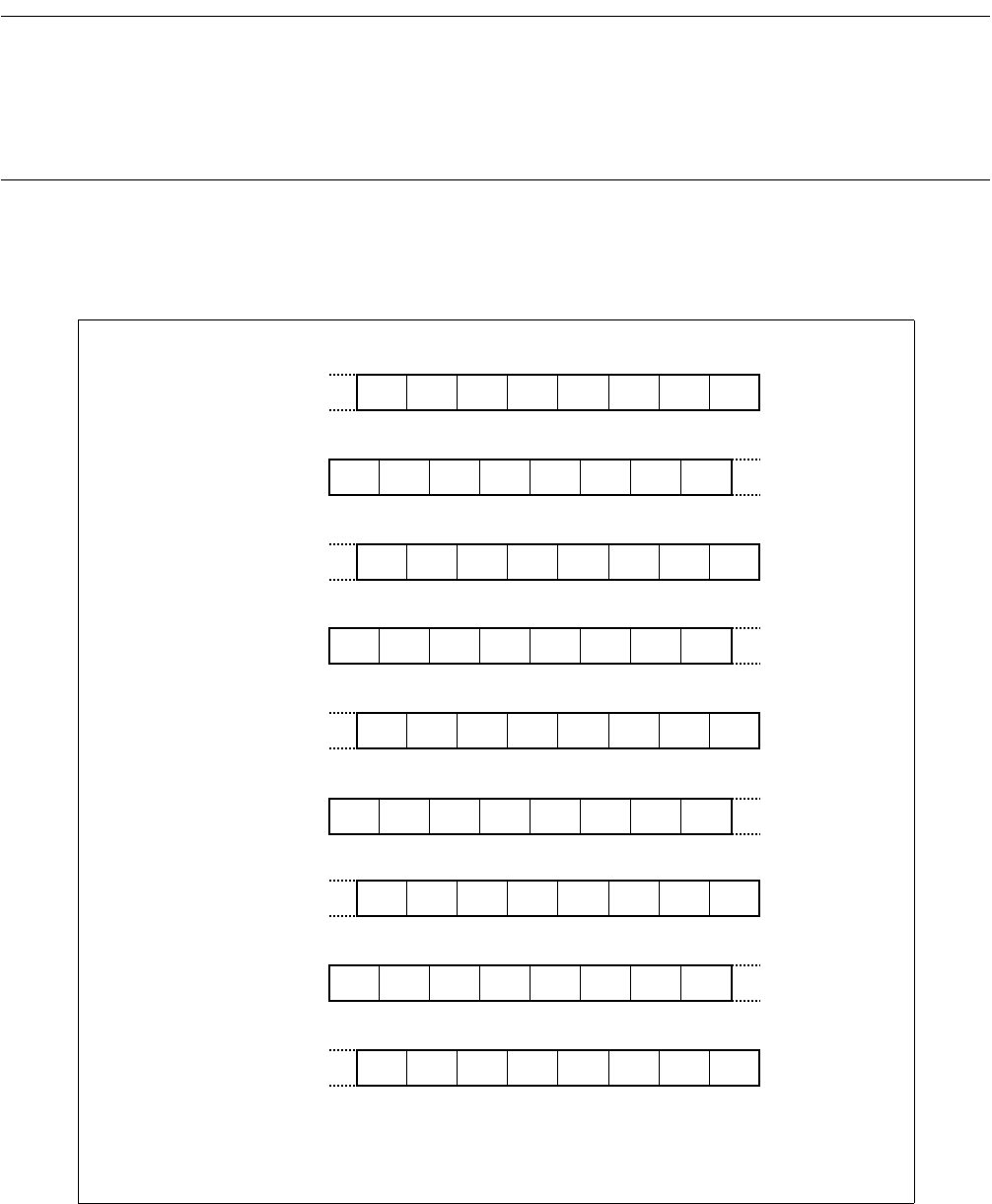

■ Detect Address Setting Registers (PADR0 to PADR5)

Figure 22.3-4 Detect Address Setting Registers (PADR0 to PADR5)

R/W R/WR/WR/WR/W R/WR/WR/W

D11 D8D9D10D15 D12D13D14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

R/W R/WR/WR/WR/W R/WR/WR/W

D19 D16D17D18D23 D20D21D22

D19 D16D17D18D23 D20D21D22

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

R/W R/WR/WR/WR/W R/WR/WR/W

D3 D0D1D2D7 D4D5D6

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0079F8H

0079F7H

0079E7H

0079F6H

0079E6H

0079F2H

0079E2H

0079F1H

0079E1H

0079F0H

0079E0H

0079F5H

0079E5H

0079F4H

0079E4H

0079F3H

0079E3H

R/W R/WR/WR/WR/W R/WR/WR/W

D11 D8D9D10D15 D12D13D14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

R/W R/WR/WR/WR/W R/WR/WR/W

D3 D0D1D2D7 D4D5D6

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

R/W R/WR/WR/WR/W R/WR/WR/W

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

R/W R/WR/WR/WR/W R/WR/WR/W

D11 D8D9D10D15 D12D13D14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

R/W R/WR/WR/WR/W R/WR/WR/W

D19 D16D17D18D23 D20D21D22

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

R/W R/WR/WR/WR/W R/WR/WR/W

D3 D0D1D2D7 D4D5D6

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0079E8H

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

PADR5: High

PADR2: High

Address

Reset value

Reset value

Reset value

Reset value

Reset value

Reset value

Reset value

Reset value

Reset value

PADR5: Middle

PADR2: Middle

PADR5: Low

PADR2: Low

PADR4: High

PADR1: High

PADR4: Middle

PADR1: Middle

PADR4: Low

PADR1: Low

PADR3: High

PADR0: High

PADR3: Middle

PADR0: Middle

PADR3: Low

PADR0: Low

R/W : Read/Write

X : Undefined