483

21.4.24 ID Register x (x = 0 to 15) (IDRx)

This register is the ID register for message buffer (x).

■ Register Configuration

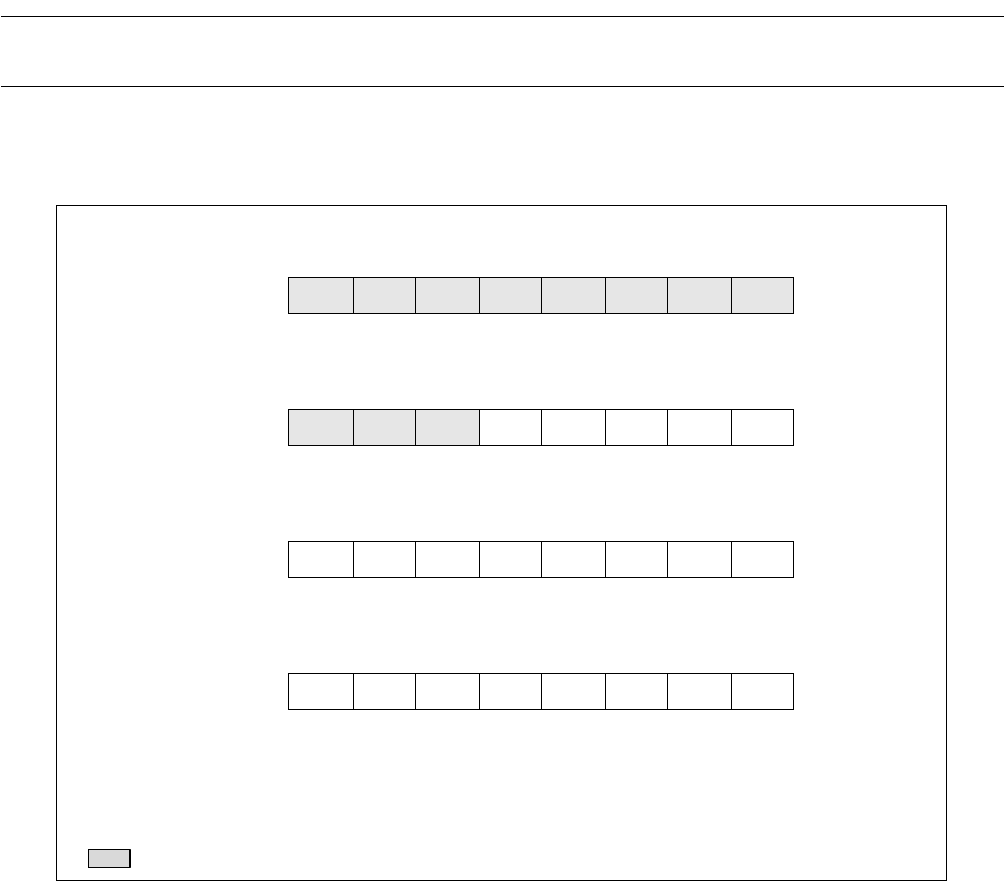

Figure 21.4-24 Configuration of the ID Registers (IDRx)

Address bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 IDRx1(Byte0)

CAN1: 007C20

H

+ 4 × x ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21 Reset value

XXXXXXXX

B

R/W R/W R/W R/W R/W R/W R/W R/W

Address bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8 IDRx1(Byte1)

CAN1: 007C21

H

+ 4 × x ID20 ID19 ID18 ID17 ID16 ID15 ID14 ID13 Reset value

XXXXXXXX

B

R/W R/W R/W R/W R/W R/W R/W R/W

Address bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 IDRx1(Byte2)

CAN1: 007C22

H

+ 4 × x ID12 ID11 ID10 ID9 ID8 ID7 ID6 ID5 Reset value

XXXXXXXX

B

R/W R/W R/W R/W R/W R/W R/W R/W

Address bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8 IDRx1(Byte3)

CAN1: 007C23

H

+ 4 × x ID4 ID3 ID2 ID1 ID0 −−−Reset value

XXXXXXXX

B

R/W R/W R/W R/W R/W −−−

x = 0, ..., 15

R/W

X

−

: Read/Write

: Undefined

: Unused

: Used bit in typical frame format