303

CHAPTER 16 8-/16-BIT PPG TIMER

●

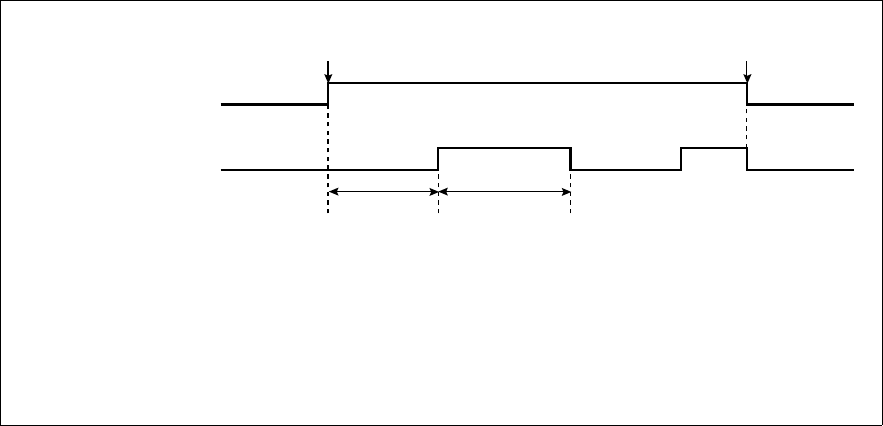

Output waveform in 8-bit PPG output 2-channel independent operation mode

The High and Low pulse widths to be outputted are determined by adding 1 to the value in the PPG reload

register and multiplying it by the count clock cycle. For example, if the value in the PPG reload register is

"00

H

", the pulse width has one count clock cycle, and if the value is "FF

H

", the pulse width has 256 count

clock cycles.

The equations for calculating the pulse width are shown below:

P

L

=T × (L+1)

P

H

=T × (H+1)

P

L

: Low width of output pulse

P

H

: High width of output pulse

L: Values of 8 bits in PPG reload register (PRLLn or PRLLm)

H: Values of 8 bits in PPG reload register (PRLHn or PRLHm)

T: Count clock cycle

Figure 16.5-3 shows the output waveform in the 8-bit PPG output 2-channel independent operation mode.

Figure 16.5-3 Output Waveform in 8-bit PPG Output 2-channel Independent Operation Mode

T × (L + 1)

T × (H + 1)

Operating start Operating stop

PPG operating enable

bit (PEN)

PPG output pin

L : Value of PPG reload register (PRLL)

H : Value of PPG reload register (PRLH)

T : Count clock cycle

Note: n = C, E

m = n + 1