153

CHAPTER 8 LOW-POWER CONSUMPTION MODE

●

Status of pins

Whether the I/O pins in the stop mode retain the state they had immediately before switching to the stop

mode or go to the high-impedance state can be controlled by the SPL bit of the low-power consumption

mode control register (LPMCR).

Note:

For those external pins shared between port functions and peripheral functions, disable output for the

peripheral functions then set the STP bit to "1" to set these pins in high impedance state.

■ Return from Stop Mode

The stop mode is cancelled by a reset factor or when an interrupt is generated. At return from the stop

mode, the oscillation clock (HCLK) and the sub clock (SCLK) stop, so the stop mode is cancelled after the

elapse of the main clock oscillation stabilization wait time or the sub clock oscillation stabilization wait

time.

●

Return by reset factor

When the stop mode is cancelled by a reset factor, the main clock oscillation stabilization wait time is

generated. After the termination of the main clock oscillation stabilization wait time, the stop mode is

cancelled, transiting to the reset sequence.

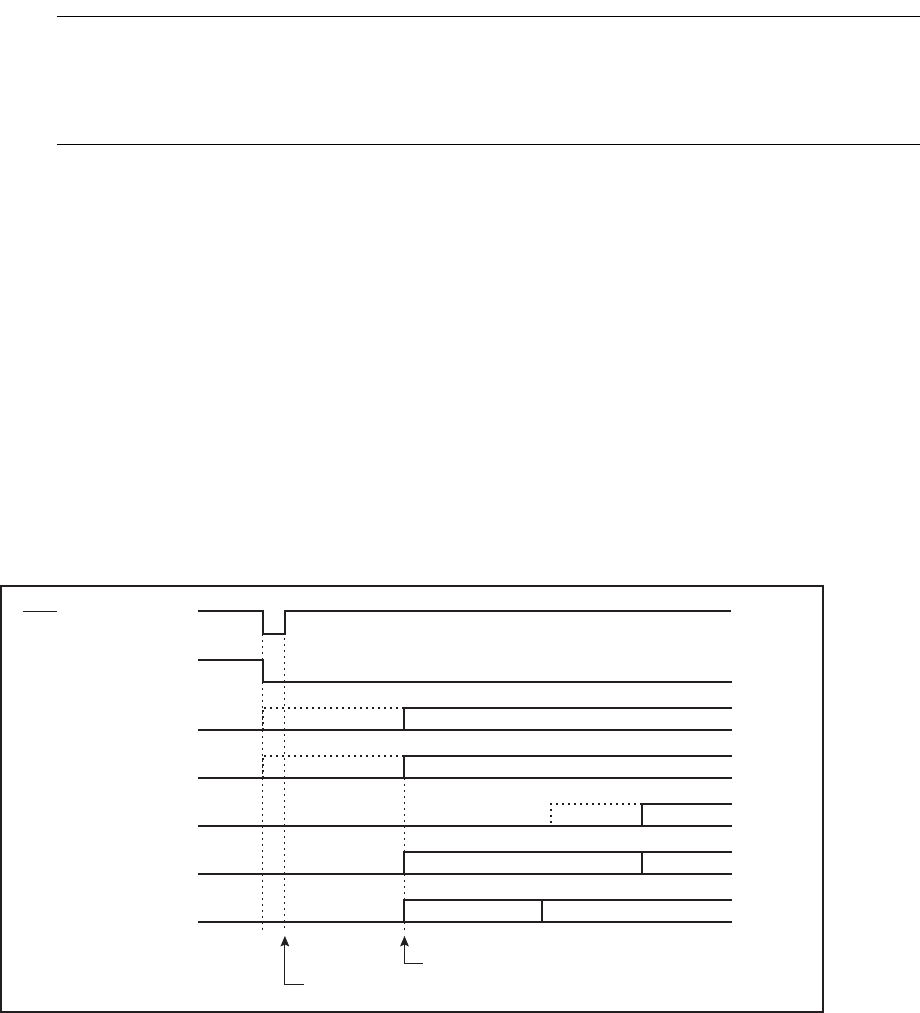

Figure 8.5-2 shows the return from the sub-stop mode by an external reset.

Figure 8.5-2 Return from the Sub-stop Mode by an External Reset

RST pin

Stop mode

Subclock

PLL clock

Main clock

CPU operation clock

Main clock

PLL clock

CPU operation

During stop Reset sequence Normal process

Cancellation of reset

Cancellation of stop mode

Oscillation

stabilization wait

During oscillation

Oscillation stabilization wait

During oscillation

Oscillation stabilization wait

During oscillation