29

CHAPTER 2 CPU

2.2 Memory Space

An F

2

MC-16LX CPU has a 16M bytes memory space. All data program input and output

managed by the F

2

MC-16LX CPU are located in this 16M bytes memory space. The CPU

accesses the resources by indicating their addresses using a 24-bit address bus.

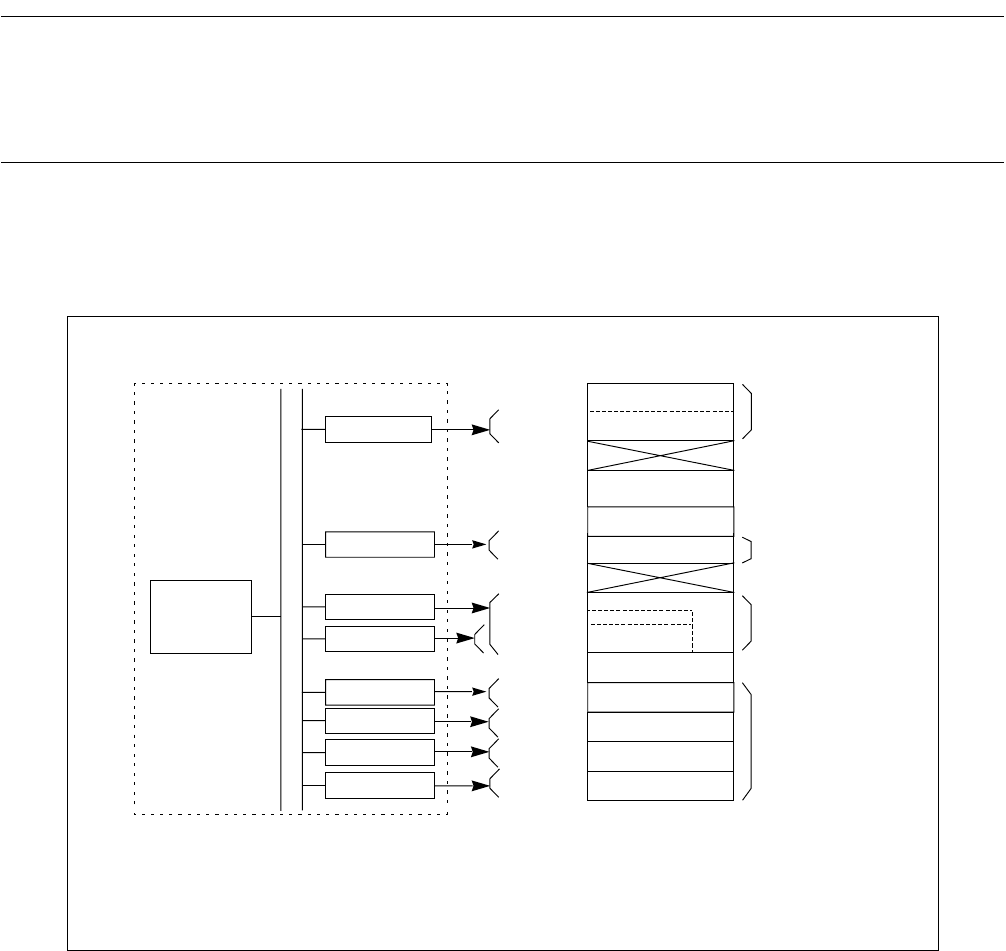

■ Outline of CPU Memory Space

Figure 2.2-1 shows a sample relationship between the F

2

MC-16LX system and memory map.

Figure 2.2-1 Sample Relationship between F

2

MC-16LX System and Memory Map

FFFFFF

H

FFFC00

H

010000

H

100000

H

000380

H

000180

H

000100

H

0000F0

H

0000C0

H

0000B0

H

000020

H

000000

H

007900

H

FF0000

H

*1

001900

H

*2

008000

H

F

2

MC-16LX device

F

2

MC-16LX

CPU

EI

2

OS

EI

2

OS

descriptor area

Programs

Peripheral circuit

Peripheral circuit

Data

Internal data bus

Interrupt

General-purpose

ports

Vector table area

Peripheral function

control register area

Peripheral function control

register area

Interrupt control

register area

Peripheral function control

register area

I/O port control

register area

Program area

ROM area

(FF bank image)

Data area

External area

*3

External area

*3

General-purpose register

ROM area

I/O area

RAM area

I/O area

Peripheral circuit

*1: The size of the internal ROM differs for each model.

*2: The size of the internal RAM differs for each model.

*3: Access is not possible in single-chip mode.