47

CHAPTER 2 CPU

2.8-1 . DPR is eight bits long, and is initialized to 01

H

by a reset. DPR can be read or written to by an

instruction.

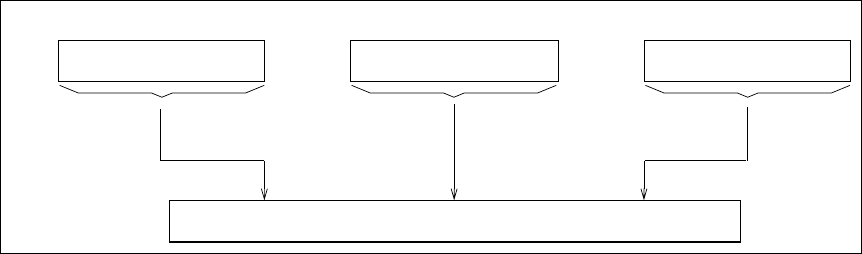

Figure 2.8-1 Generating a Physical Address in Direct Addressing Mode

●

Program counter bank register (PCB) <Initial value: Value in reset vector>

●

Data bank register (DTB) <Initial value: 00

H

>

●

User stack bank register (USB) <Initial value: 00

H

>

●

System stack bank register (SSB) <Initial value: 00

H

>

●

Additional data bank register (ADB) <Initial value: 00

H

>

Each bank register indicates the memory bank where the PC, DT, SP (user), SP (system), or AD space is

allocated. All bank registers are one byte long. PCB is initialized to 00

H

by a reset. Bank registers other

than PCB can be read or written to. PCB can be read but cannot be written to.

PCB is updated when the JMPP, CALLP, RETP, RETIQ, or RETF instruction branching to the entire 16M

bytes space is executed or when an interrupt occurs. For operation of each register, see "2.2 Memory

Space".

α α α α α α α α β β β β β β β β γ γ γ γ γ γ γ γ

α α α α α α α α β β β β β β β β γ γ γ γ γ γ γ γ

MSB LSB

DTB register

DPR register

Direct address during instruction

24-bit physical address