143

CHAPTER 8 LOW-POWER CONSUMPTION MODE

8.5 Standby Mode

The standby mode causes the standby control circuit to either stop supplying an

operation clock to the CPU or peripheral functions or to stop the oscillation clock

reducing power consumption.

■ Operation Status during Standby Mode

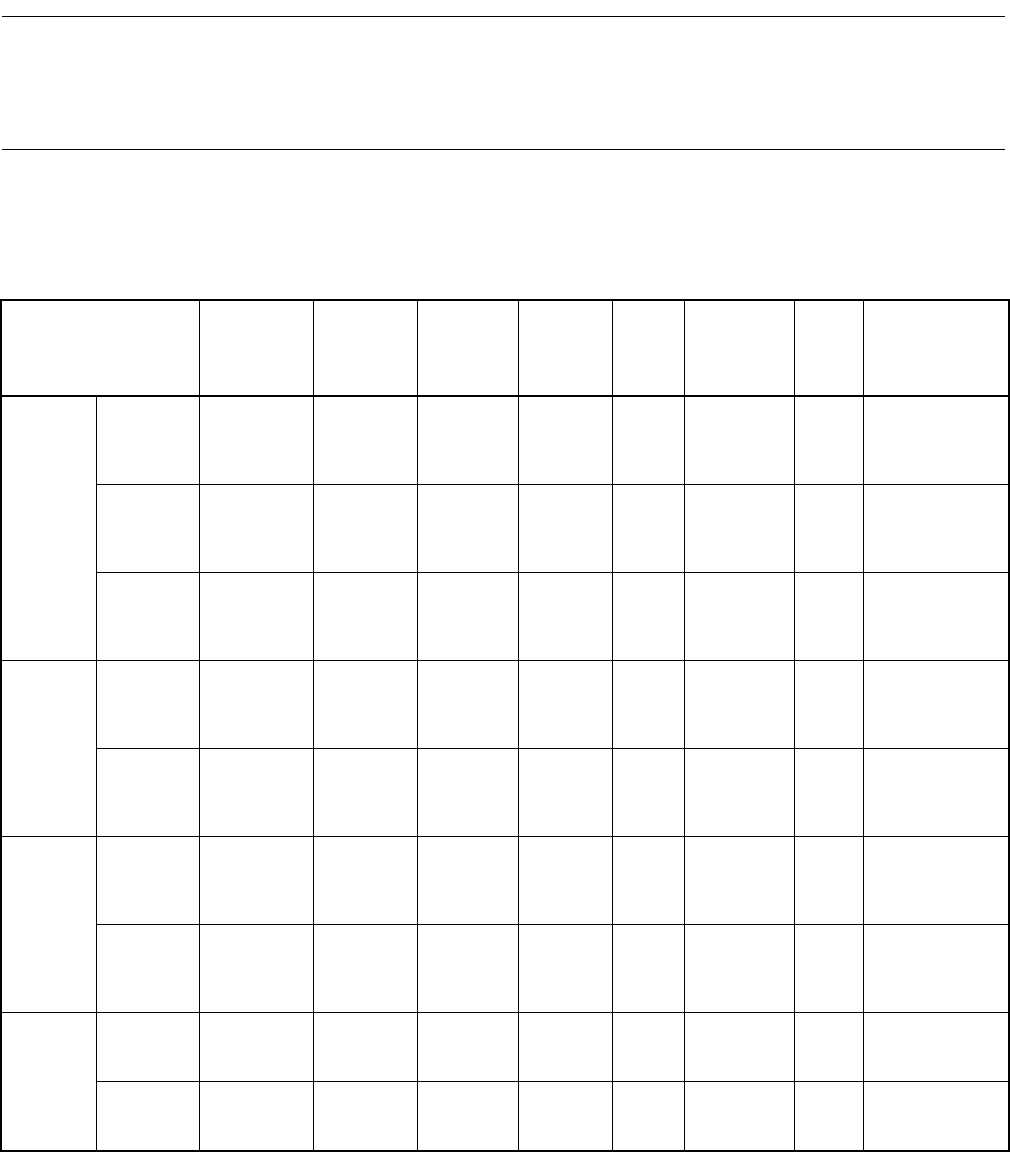

Table 8.5-1 shows operation status during standby mode.

Table 8.5-1 Operation Status during Standby Mode

Mode name Transition

conditions

Oscillation

clock

(HCLK)

Sub-clock

(SCLK)

Machine

clock

CPU Peripheral

function

Pin Release

method

Sleep

mode

Main sleep

mode

MCS=1

SCS=1

SLP=1

❍❍❍✕❍❍

External reset or

interrupt

Sub-sleep

mode

MCS=X

SCS=0

SLP=1

✕❍❍✕❍❍

External reset or

interrupt

PLL sleep

mode

MCS=0

SCS=1

SLP=1

❍❍❍✕❍❍

External reset or

interrupt

Timebase

timer

mode

SPL=0 MCS=X

SCS=1

TMD=0

❍❍✕✕

✕

*1

◆

External reset or

interrupt

*4

SPL=1 MCS=X

SCS=1

TMD=0

❍❍✕✕

✕

*1

Hi-Z

*3

External reset or

interrupt

*4

Watch

mode

SPL=0 MCS=X

SCS=0

TMD=0

✕❍✕✕

✕

*2

◆

External reset or

interrupt

*5

SPL=1 MCS=X

SCS=0

TMD=0

✕❍✕✕

✕

*2

Hi-Z

*3

External reset or

interrupt

*5

Stop

mode

SPL=0 STP=1

✕✕✕✕✕◆

External reset or

interrupt

*6

SPL=1 STP=1

✕✕✕✕✕

Hi-Z

*3

External reset or

interrupt

*6