638

APPENDIX

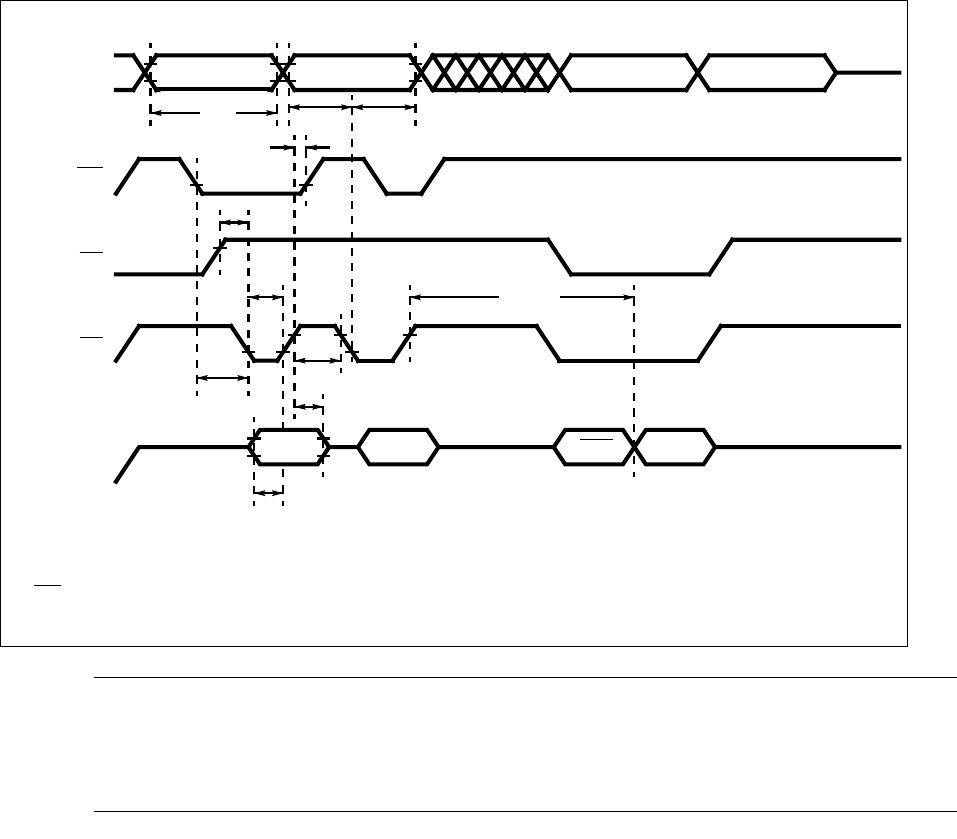

■ Write, Data Polling, Read (CE control)

Figure C-3 Timing Diagram for Write Access (CE control)

Note:

• Describes the last 2-bus cycle of 4-bus cycle sequences.

• "Fx" in "FxAAAA" described as address is any of F.

A

Q18 to AQ0

WE

OE

CE

DQ7

to DQ0

t

WC

PA

t

AS

t

AH

PA

t

WHWH1

t

CP

t

WS

t

CPH

t

DH

t

DS

A0

H

PD

DQ7

t

GHWL

t

WH

Dout

FxAAAA

H

3rd bus cycle

Data polling

PA : Write address

PD : Write data

DQ

7

: Reverse output of write data

D

OUT

: Output of write data