6-5

BUS INTERFACE UNIT

6.2 BUS OPERATION

The processor generates eight different types of bus operations:

• Memory data read (data fetch)

• Memory data write

• Memory code read (instruction fetch)

• I/O data read (data fetch)

• I/O data write

• Halt or shutdown

• Refresh

• Interrupt acknowledge

These operations are defined by the states of four bus status pins: M/IO#, D/C#, W/R# and RE-

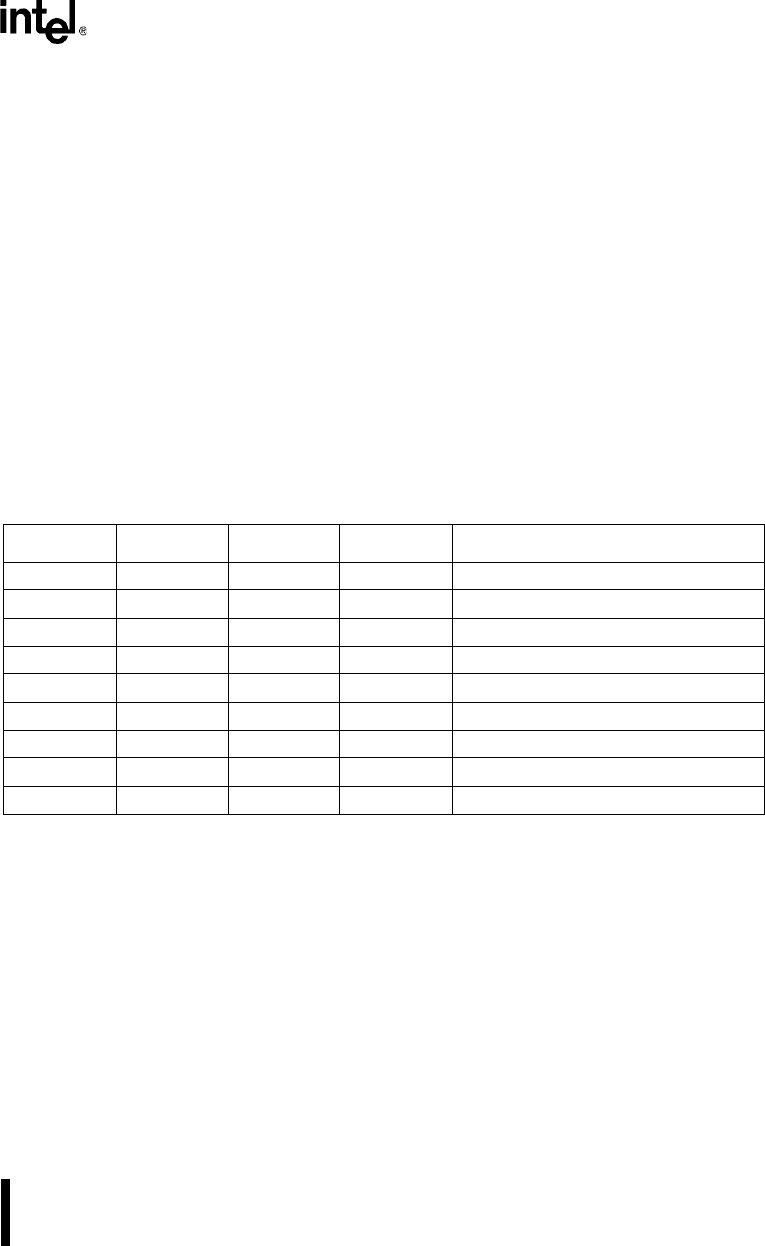

FRESH#. Table 6-2 lists the various combinations and their definitions.

Table 6-2. Bus Status Definitions

M/IO# D/C# W/R# REFRESH# Bus Operation

0 0 0 1 interrupt acknowledge cycle

0 0 1 1 never occurs

0 1 0 1 I/O data read

0 1 1 1 I/O data write

1 0 0 1 memory code read

1 0 1 1 halt or shutdown cycle*

1 1 0 0 refresh cycle

1 1 0 1 memory data read

1 1 1 1 memory data write

*The byte address is 2 for a halt and 0 for a shutdown. For both conditions, BHE# is high and BLE# is low.