Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

5-22

Setting bit 0 in the PORT92 register (see Figure 5-14) resets the core without resetting the periph-

erals. Unlike the RESET pin, which is asynchronous and can be used to synchronize internal

clocks to CLK2, this core-only reset is synchronized with the on-chip clocks and does not affect

the on-chip clock synchronization. After the CPU-RESET this bit is still set to 1. It must be

cleared and then set to cause another core-only reset.

Clearing bit 1 in the PORT92 register forces address line A20 to 0. This bit affects only addresses

generated by the core; addresses generated by the DMA and the refresh control unit are not af-

fected.

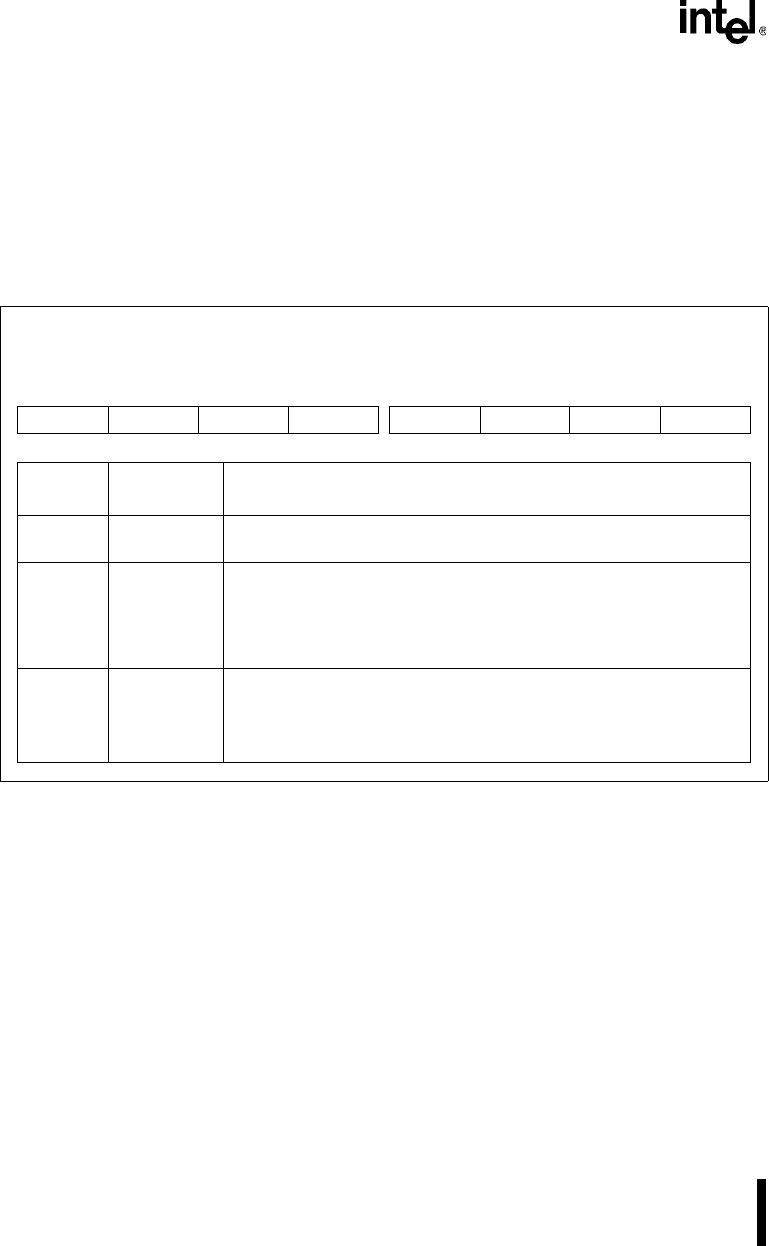

Figure 5-14. Port 92 Configuration Register (PORT92)

Port 92 Configuration

PORT92

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F092H

0092H

XXXXXX10B

7 0

— — — — — — A20G CPURST

Bit

Number

Bit

Mnemonic

Function

7–2 — Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

1 A20G A20 Grounded:

0 = Clearing this bit forces address line A20 to 0. This bit affects

addresses generated only by the core. Addresses generated by the

DMA and the Refresh Unit are not affected by this bit.

1 = Setting this bit leaves core-generated addresses unmodified.

0 CPURST CPU Reset:

0 = Clearing this bit performs no operation.

1 = Setting this bit resets the core without resetting the peripherals.

This bit must be cleared before issuing another reset.