D-61

SYSTEM REGISTER QUICK REFERENCE

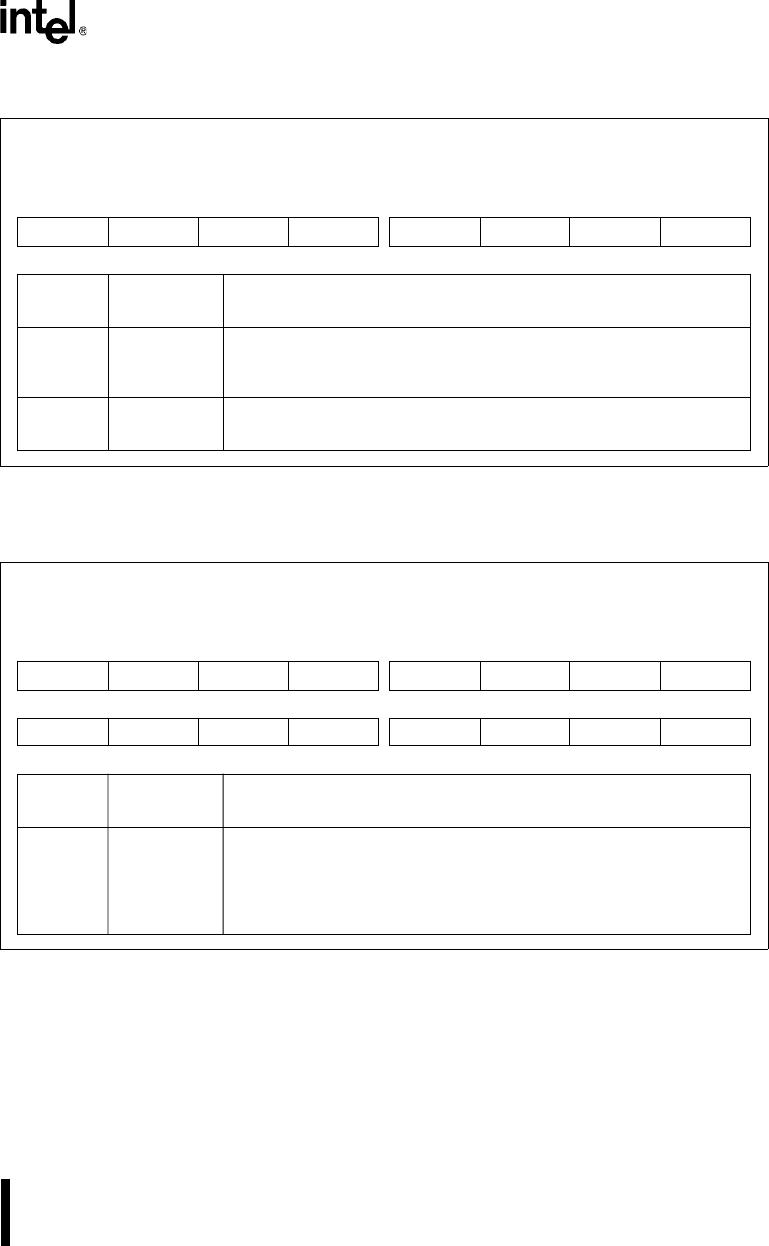

D.61 SSIOCTR

D.62 SSIORBUF

Baud-rate Count Down

SSIOCTR

(read only)

Expanded Addr:

ISA Addr:

Reset State:

F48AH

—

00H

7 0

BSTAT CV6 CV5 CV4 CV3 CV2 CV1 CV0

Bit

Number

Bit

Mnemonic

Function

7 BSTAT Baud-rate Generator Status:

0 = The baud-rate generator is disabled.

1 = The baud-rate generator is enabled.

6–0 CV6:0 Current Value:

These bits indicate the current value of the baud-rate down counter.

Receive Holding Buffer

SSIORBUF

(read only)

Expanded Addr:

ISA Addr:

Reset State:

F482H

—

0000H

15 8

RB15 RB14 RB13 RB12 RB11 RB10 RB9 RB8

7 0

RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0

Bit

Number

Bit

Mnemonic

Function

15–0 RB15:0 Receive Buffer Bits:

This register contains the last word received. The receive shift register

shifts bits in with the rising edge of the receiver clock pin. Data is shifted

in starting with the most-significant bit. The control logic then transfers

the received word from the receive shift register to SSIORBUF.