Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

8-6

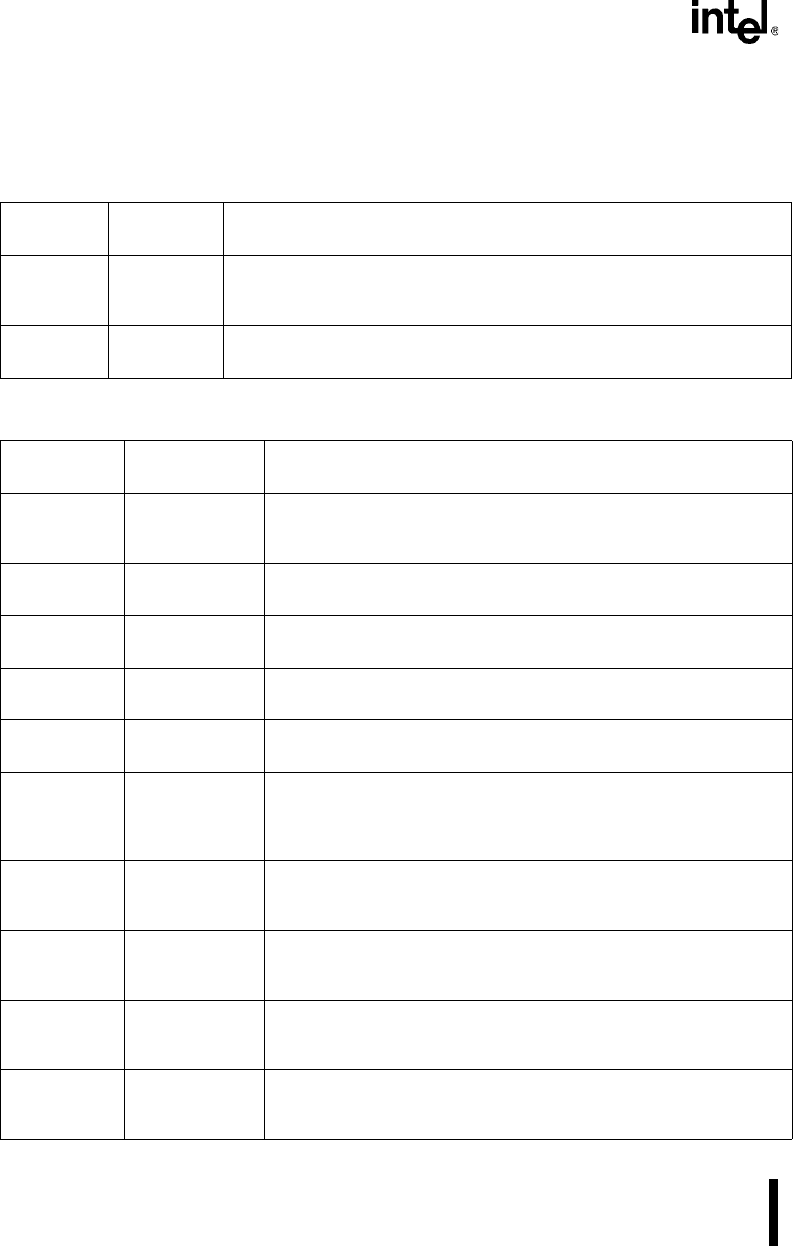

8.1.3 Clock and Power Management Registers and Signals

Table 8-1 lists the registers and Table 8-2 list the signals associated with the clock and power man-

agement unit.

Table 8-1. Clock and Power Management Registers

Register

Expanded

Address

Description

CLKPRS 0F804H

Clock Prescale:

This register contains the programmed divisor value used to generate PSCLK

from the internal clock.

PWRCON 0F800H

Power Control:

This register selects the power management mode and internal ready options.

Table 8-2. Clock and Power Management Signals

Signal

Device Pin or

Internal Signal

Description

CLK2 Device pin

Input Clock:

Connect an external clock to this pin to provide the fundamental timing for

the microprocessor.

CLKOUT Device pin

Output Clock:

CLKOUT is a Phase 1 output clock (PH1P)

IDLE Internal signal

Idle Output (to the Watchdog Timer Unit):

IDLE indicates that the device is in idle mode.

INTR Internal signal

Interrupt Input (from the Interrupt Control Unit):

INT causes the device to exit powerdown or idle mode.

NMI Device pin

Nonmaskable Interrupt Input:

NMI causes the device to exit powerdown or idle mode.

PSCLK Internal signal

Prescaled Clock Output:

PSCLK is one of two possible clock inputs for the SSIO baud-rate

generator and the Timer/counter Unit. The PSCLK frequency is controlled

by the CLKPRS register.

PWRDOWN Device pin

Powerdown Output (multiplexed with P3.6):

A high state on the PWRDOWN pin indicates that the device is in

powerdown mode.

RESET Device pin

System Reset Input:

This signal resets the processor and causes the device to exit powerdown

or idle mode.

SERCLK Internal signal

Serial Clock Output:

SERCLK is one of two possible clock inputs for the SIO or SSIO baud-

rate generator. The SERCLK frequency is one-fourth the CLK2 frequency.

SMI# Device pin

System Management Interrupt Input:

SMI# causes the device to exit powerdown or idle mode and causes the

processor to enter System Management Mode.