Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

6-8

Memory read and memory write cycles can be locked to prevent another bus master from using

the local bus. This allows for indivisible read-modify-write operations.

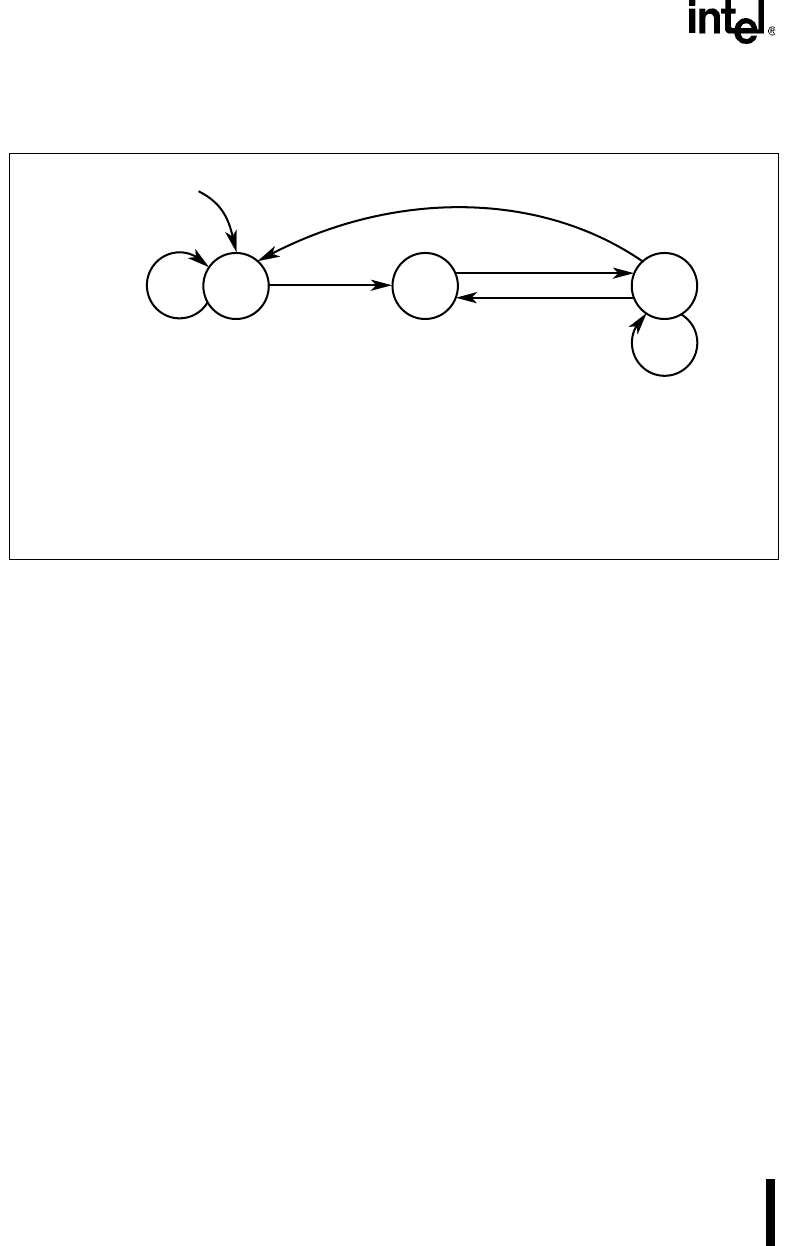

Figure 6-2. Simplified Bus State Diagram

(Does Not Include Address Pipelining or Hold states)

6.2.2 Pipelining

The processor can control the address and status outputs so that the outputs for the next bus cycle

become valid before the end of the present bus cycle. This technique, allowing bus cycles to over-

lap, is called pipelining.

Pipelining increases bus throughput without decreasing allowable memory or I/O access time,

thus allowing high bandwidth with relatively slow, inexpensive components. In addition, using

pipelining to address slower devices can yield the same throughput as addressing faster devices

with no pipelining. With pipelining, a device operating at 33 MHz (CLK2 = 66 MHz) can transfer

data at 33 Mbytes per second while requiring a device with access time of approximately 3 T-

states (90 ns at 33 MHz, neglecting signal delays). Without address pipelining, the access time

has to be approximately 2 T-states (60 ns at 25 MHz). Therefore, when pipelining is used, slower

devices can be used in the system to achieve performance similar to a faster device in a non-pipe-

lined system.

Pipelining is not supported during I/O bus cycles and BS8 cycles (16-bit accesses to 8-bit devic-

es).

NOTE

During I/O cycles, NA# is ignored. NA# must be kept deasserted (blocked

externally) during the T2 states of BS8 memory cycles.

Bus States:

T1 - First clock of a non-pipelined bus cycle (CPU drives

new address and asserts ADS#).

T2 - Subsequent clocks of a bus cycle when NA# has not

been sampled asserted in the current bus cycle.

Ti - Idle State

The fastest bus cycle consists of two states: T1 and T2.

Ti T2

A2484-02

T1

READY# Asserted • No Request

READY# Asserted •

Request Pending

No Request

READY# Negated

Always

Request Pending

Reset Asserted