E-23

INSTRUCTION SET SUMMARY

E.2.1 32-bit Extensions of the Instruction Set

With the Intel386 EX processor the 8086/80186/80286 instruction set is extended in two orthog-

onal directions: 32-bit forms of all 16-bit instructions are added to support the 32-bit data types,

and 32-bit addressing modes are made available for all instructions referencing memory. This or-

thogonal instruction set extension is accomplished having a Default (D) bit in the code segment

descriptor, and by having 2 prefixes to the instruction set.

The instruction defaults to operations of 16 bits or 32 bits, depending on the setting of the D bit

in the code segment descriptor, which gives the default length (either 32 bites or 16 bits) for both

operands and effective addresses when executing that code segment. In the Real Address Mode

or Virtual 8086 Mode, no code segment descriptors are used, but a D value of 0 is assumed inter-

nally by the Intel386 EX processor when operating in those modes (for 16-bit default sizes com-

patible with the 8086/80186/80286).

Two prefixes, the Operand Size Prefix and the Effective Address Size Prefix, allow overriding

individually the Default selection of operand size and effective address size. These prefixes may

precede any opcode bytes and affect only the instruction they precede. If necessary, one or both

prefixes may be placed before the opcode bytes. The presence of the Operand Size Prefix and the

Effective Address Prefix toggles the operand size or the effective address size, respectively, to the

value “opposite” from the default setting. For example, if the default operand size is for 32-bit

data operations, then presence of the Operand Size Prefix toggles the instruction to use 32-bit ef-

fective address computations.

These 32-bit extensions are available in all modes, including the Real Address Mode or the Vir-

tual 8086 Mode. In these modes the default is always 16 bits, so prefixes are needed to specify

32-bit operands or addresses. For instructions with more than one prefix the order of prefixes is

unimportant.

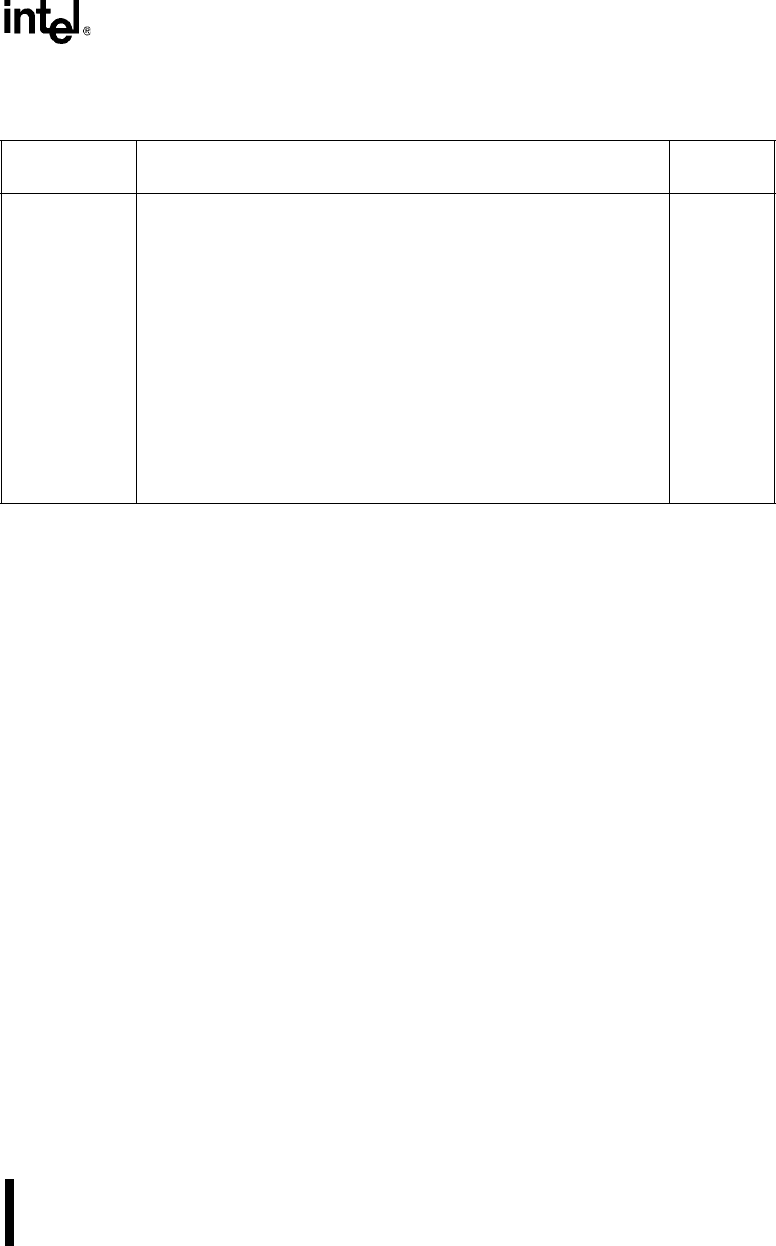

Table E-2. Fields Within Instructions

Field Name Description

Number of

Bits

w

d

s

reg

mod r/m

ss

index

base

sreg2

sreg3

tttn

Specifies if data is byte of full size (full size is either 16 or 32 bits)

Specifies Direction of Data Operation

Specifies if an Immediate Data Field must be Sign-Extended

General Register Specifier

Address Mode Specifier (Effective Address can be a General Register)

Scale Factor for Scaled Index Address Mode

General Register to be used as Index Register

General Register to be used as Base Register

Segment Register Specifier for CS, SS, DS, ES

Segment Register Specifier for CS, SS, DS, ES, FS, GS

For Conditional Instructions, specifies a condition asserted

or a condition negated

1

1

1

3

2 for mod:

3 for r/m

2

3

3

2

3

4

NOTE: Figure E-1 shows encoding of individual instructions.