7-11

SYSTEM MANAGEMENT MODE

then any pending INTR and NMI is serviced after completion of RSM instruction execution.

Only one INTR and one NMI can be pending.

The SMM handler may choose to enable interrupts to take advantage of device drivers. Since in-

terrupts were enabled while under control of the SMM handler, the signal SMIACT# continues

to be asserted. If the system designer wants to take advantage of existing device drivers that le-

verage interrupts, the memory controller must take this into account.

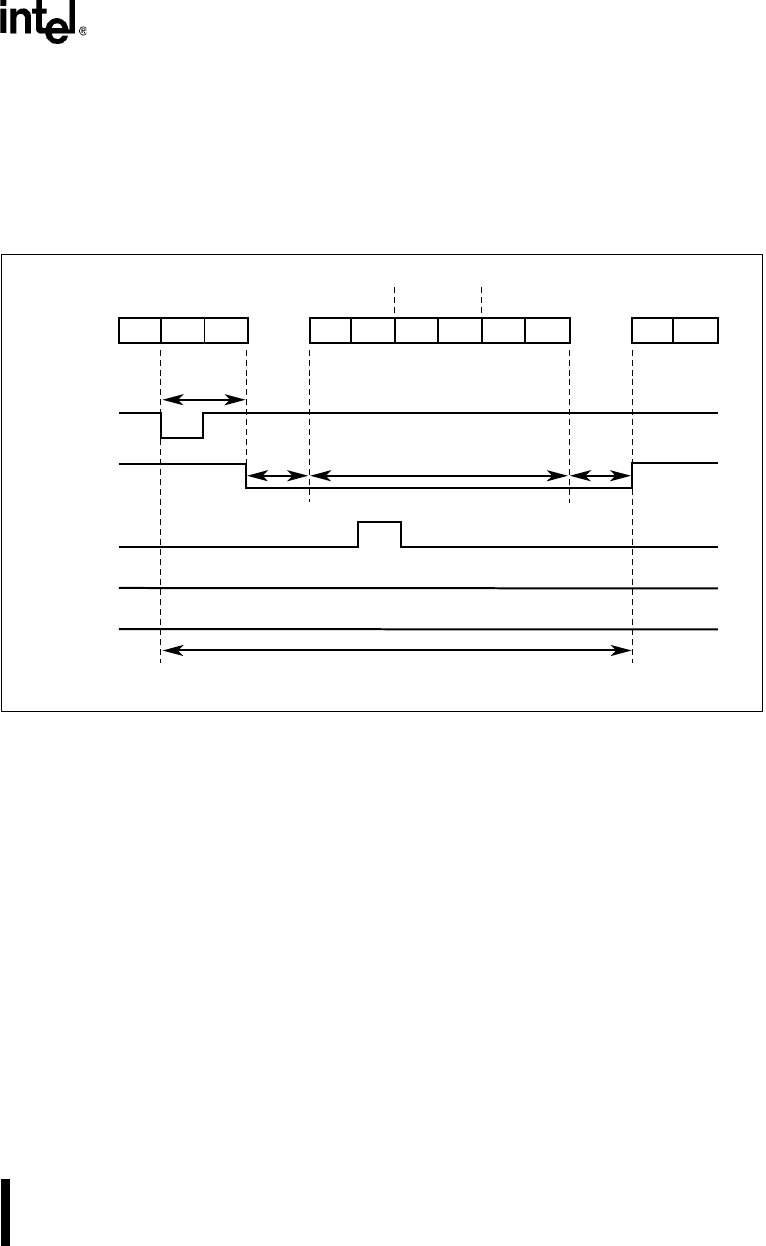

Figure 7-6. Interrupted SMI# Service

7.3.3.2 HALT During SMM Handler

The system designer may wish to place the system into a HALT condition while in SMM. The

CPU allows this condition to occur; however, unlike a HALT while in normal mode, the CPU in-

ternally blocks INTR and NMI from being recognized until after the RSM instruction is executed.

When a HALT needs to be breakable in SMM, the SMM handler must enable INTR and NMI

before a HALT instruction execution. NMI is enabled after the completion of the first interrupt

service routine within the SMM handler.

After the SMM handler has enabled INTR and NMI, the CPU exits the HALT state and returns

to the SMM handler when INTR or NMI occurs. See Figure 7-7 for details.

A2505-02

SMI#

SMIACT#

INTR

NMI

RESET

Application

Instr

SMM

Handler

Intr

Service

SMM Handler

SMI

Latency

State

Save

RSM

State

Restore

NMI is Blocked

Instr Instr Instr Instr Instr

SMM

Handler

Instr

Instr Instr

Application

Instr

Instr