10-21

TIMER/COUNTER UNIT

.

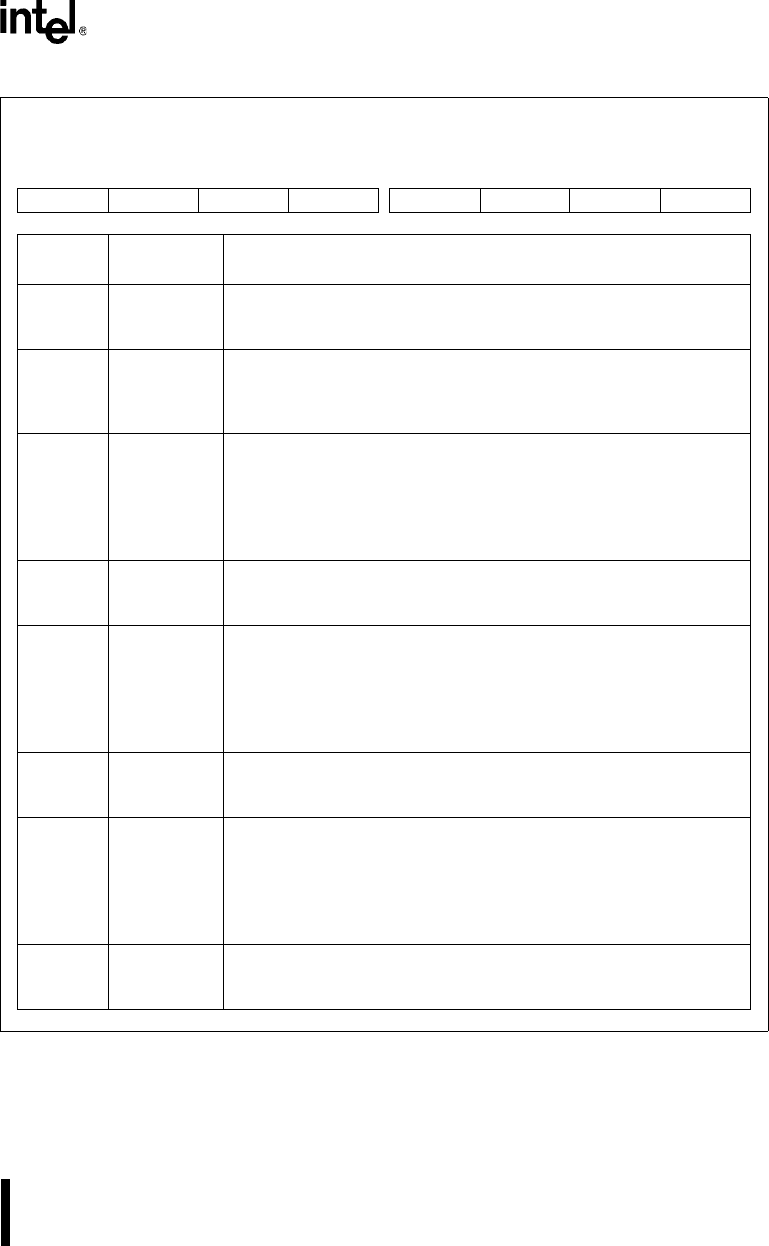

Figure 10-22. Timer Configuration Register (TMRCFG)

Timer Configuration

TMRCFG

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F834H

—

00H

7 0

TMRDIS SWGTEN GT2CON CK2CON GT1CON CK1CON GT0CON CK0CON

Bit

Number

Bit

Mnemonic

Function

7 TMRDIS Timer Disable:

0 = Enables the CLKIN

n

signals.

1 = Disables the CLKIN

n

signals.

6 SWGTEN Software GATE

n

Enable

0 = Connects GATE

n

to either the V

CC

pin or the TMRGATE

n

pin.

1 = Enables GT2CON, GT1CON, and GT0CON to control the

connections to GATE2, GATE1 and GATE0 respectively.

5 GT2CON Gate 2 Connection:

SWGTEN GT2CON

00

Connects GATE2 to V

CC.

01Connects GATE2 to the TMRGATE2 pin.

10Turns GATE2 off.

11Turns GATE2 on.

4 CK2CON Clock 2 Connection:

0 = Connects CLKIN2 to the internal PSCLK signal.

1 = Connects CLKIN2 to the TMRCLK2 pin.

3 GT1CON Gate 1 Connection:

SWGTEN GT1CON

00

Connects GATE1 to V

CC.

01Connects GATE1 to the TMRGATE1 pin.

10Turns GATE1 off.

11Turns GATE1 on.

2 CK1CON Clock 1 Connection:

0 = Connects CLKIN1 to the internal PSCLK signal.

1 = Connects CLKIN1 to the TMRCLK1 pin.

1 GT0CON Gate 0 Connection:

SWGTEN GT0CON

00

Connects GATE0 to V

CC.

01Connects GATE0 to the TMRGATE1 pin.

10Turns GATE0 off.

11Turns GATE0 on.

0 CK0CON Clock 0 Connection:

0 = Connects CLKIN0 to the internal PSCLK signal.

1 = Connects CLKIN0 to the TMRCLK0 pin.