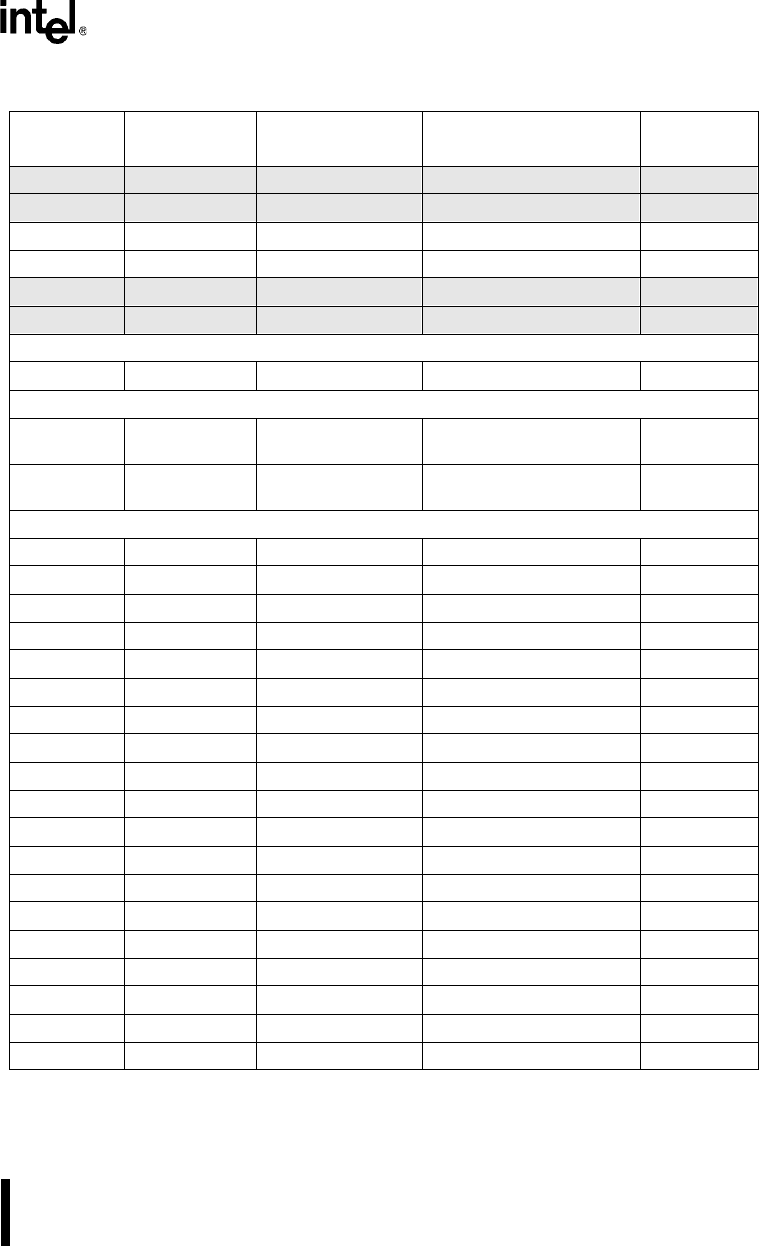

D-3

SYSTEM REGISTER QUICK REFERENCE

F08EH Reserved

F08FH Reserved

F098H Byte DMA0BYC2 XX

F099H Byte DMA1BYC2 XX

F09AH Reserved

F09BH Reserved

A20GATE and Fast CPU Reset

F092H 0092H Byte PORT92 XXXXXX10B

Slave Interrupt Controller

F0A0H 00A0H Byte ICW1s/IRRs/ISRs/

OCW2s/OCW3s

XX

F0A1H 00A1H Byte ICW2s/ICW3s/ICW4s/

OCW1s/POLLs

XX

Chip-select Unit

F400H Word CS0ADL 0000H

F402H Word CS0ADH 0000H

F404H Word CS0MSKL 0000H

F406H Word CS0MSKH 0000H

F408H Word CS1ADL 0000H

F40AH Word CS1ADH 0000H

F40CH Word CS1MSKL 0000H

F40EH Word CS1MSKH 0000H

F410H Word CS2ADL 0000H

F412H Word CS2ADH 0000H

F414H Word CS2MSKL 0000H

F416H Word CS2MSKH 0000H

F418H Word CS3ADL 0000H

F41AH Word CS3ADH 0000H

F41CH Word CS3MSKL 0000H

F41EH Word CS3MSKH 0000H

F420H Word CS4ADL 0000H

F422H Word CS4ADH 0000H

F424H Word CS4MSKL 0000H

Table D-1. Peripheral Register Addresses (Sheet 3 of 6)

Expanded

Address

PC/AT

Address

Access Type

(Byte/Word)

Register Name Reset Value

NOTES:

1. Byte pointer in flip-flop in DMA determines which register is accessed.

2. Shaded rows indicate reserved areas.