Intel386™ EX EMBEDDED PROCESSOR USER’S MANUAL

10-16

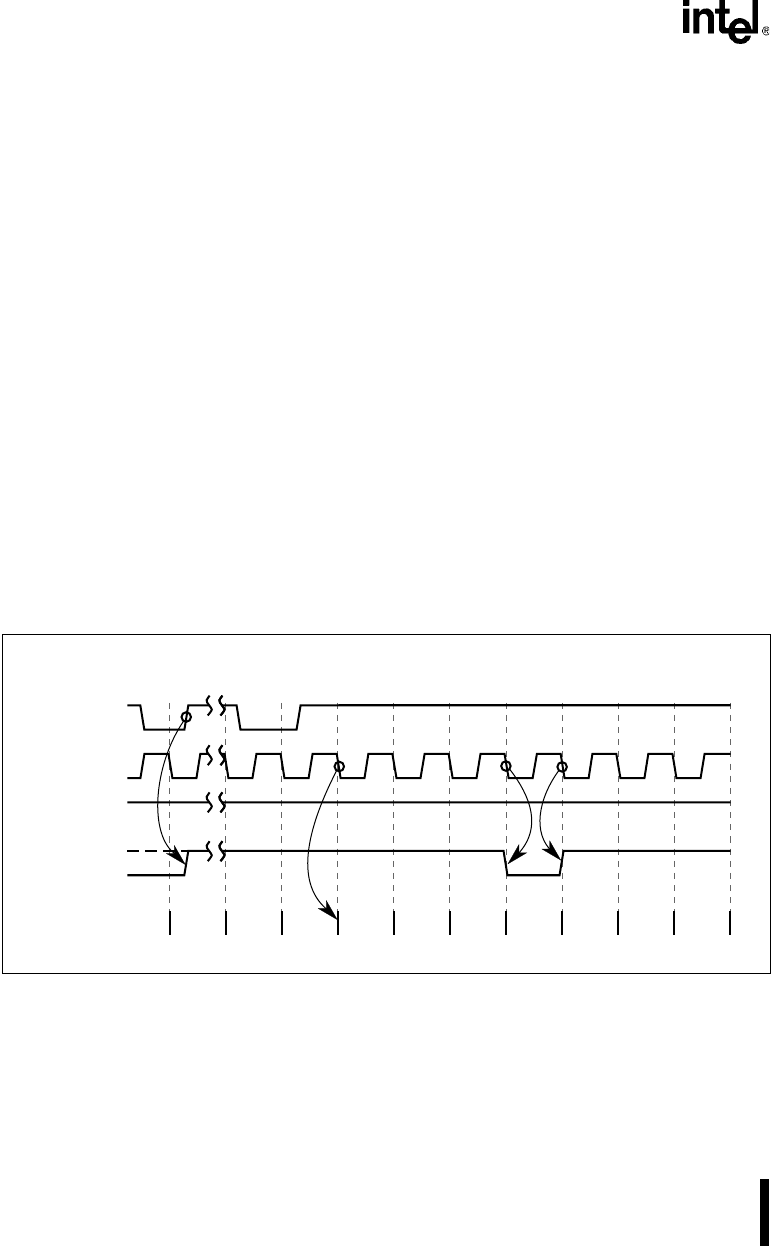

10.2.5 Mode 4 – Software-triggered Strobe

Initializing a counter for mode 4 drives the counter’s OUTn signal high and initiates counting. A

count is loaded on the CLKINn pulse following a count write. When the counter reaches zero,

OUTn strobes low for one clock pulse. The counter rolls over and continues counting, but does

not strobe low when it reaches zero again. The counter strobes low only the first time it reaches

zero after a count write. A high level on a counter’s GATEn signal enables counting; a low level

on a counter’s GATEn signal disables counting.

Mode 4’s basic operation is outlined below and shown in Figure 10-16.

1. After a control word write, OUTn is driven high.

2. On the CLKINn pulse following the count write, the count is loaded.

3. On each succeeding CLKINn pulse, the count is decremented.

4. When the count reaches zero, OUTn is driven low.

5. On the following CLKINn pulse, OUTn is driven high.

NOTE

Writing a count of N causes OUTn to strobe low in N + 1 CLKINn pulses,

provided GATEn remains high. OUTn remains low for one CLKINn pulse,

then goes high.

Figure 10-16. Mode 4 – Basic Operation

????0003 0002 0001 0000 FFFF FFFE FFFD

Writes to

Counter

n

CLKIN

n

GATE

n

OUT

n

Control

Word = 18H

Count

Count = 3

A2315-01