Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

D-26

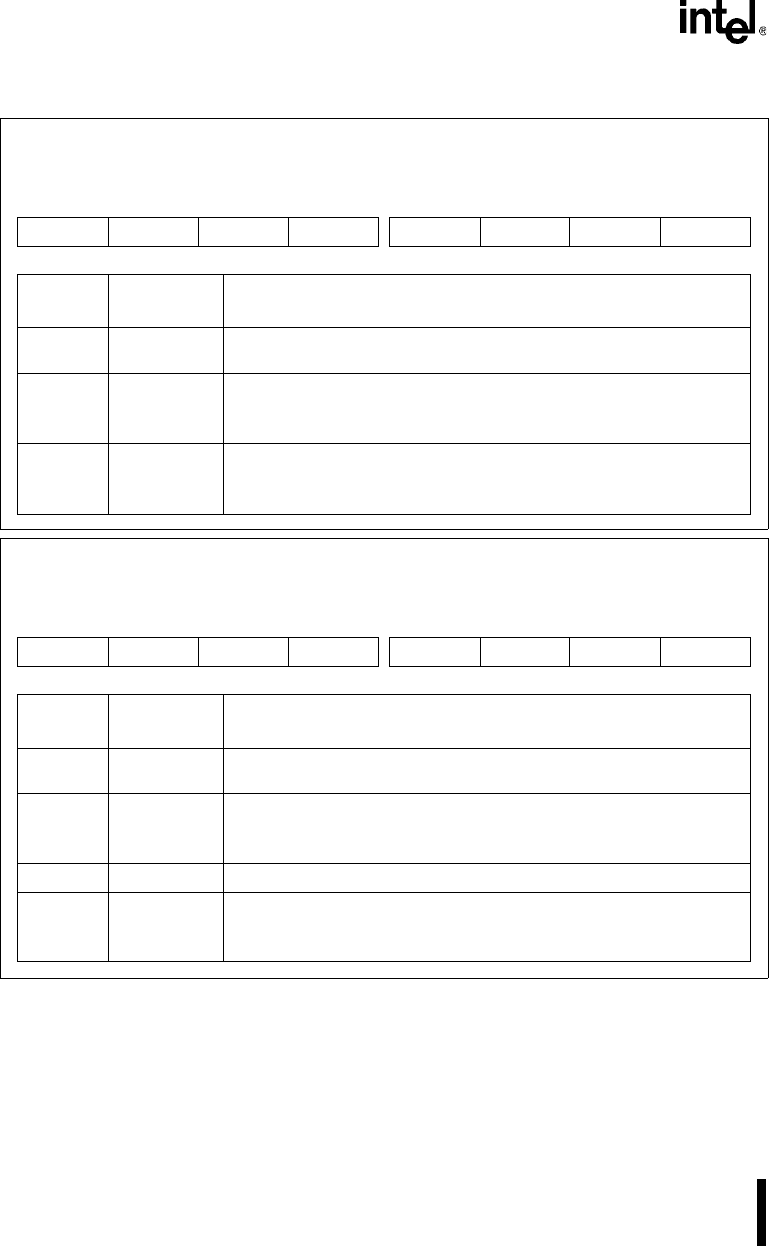

D.21 DMASRR

DMA Software Request (read format)

DMASRR

Expanded Addr:

ISA Addr:

Reset State:

F009H

0009H

00H

7 0

———— ——SR1SR0

Bit

Number

Bit

Mnemonic

Function

7–2 — Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

1 SR1 Software Request 1:

When set, this bit indicates that channel 1 has a software request

pending.

0 SR0 Software Request 0:

When set, this bit indicates that channel 0 has a software request

pending.

DMA Software Request

(write format)

DMASRR

Expanded Addr:

ISA Addr:

Reset State:

F009H

0009H

00H

7 0

———— —SR0CS

Bit

Number

Bit

Mnemonic

Function

7–3 — Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

2 SR Software Request:

Setting this bit generates a software request for the channel specified by

bit 0. When the channel’s buffer transfer completes, this bit is cleared.

1 0 Must be 0 for correct operation.

0 CS Channel Select:

0 = The selection for bit 2 affects channel 0.

1 = The selection for bit 2 affects channel 1.