Intel386™ EX EMBEDDED PROCESSOR USER’S MANUAL

10-10

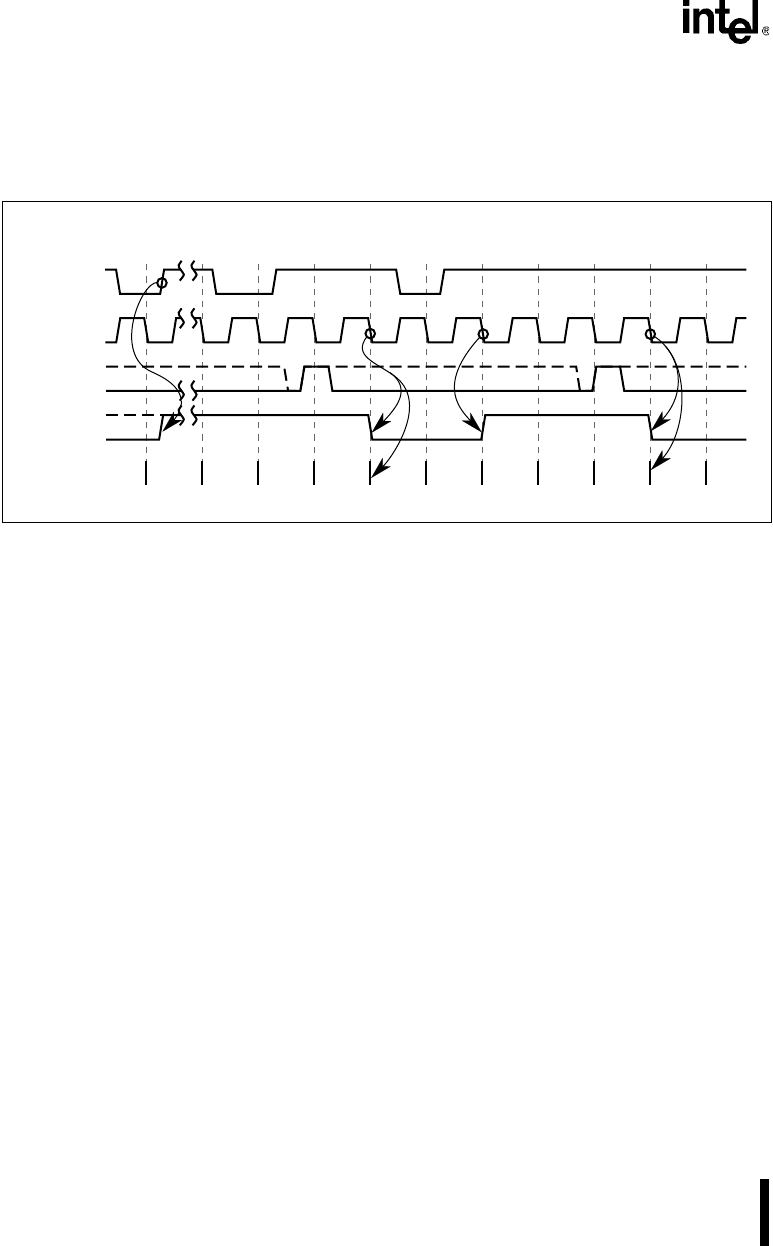

Figure 10-7 shows writing a new count. The counter waits for a gate-trigger to load the new count.

The counter loads the new count on the CLKINn pulse following the trigger, then decrements the

count on each succeeding CLKINn pulse. OUTn remains low until the count reaches zero.

Figure 10-7. Mode 1 – Writing a New Count

10.2.3 Mode 2 – Rate Generator

In this periodic mode, a counter’s OUTn signal remains high until the count reaches one, then

goes low for one clock pulse (CLKINn). After this single clock pulse, OUTn goes high and the

count is reloaded. The cycle then repeats. You can use a gate-trigger to reload the count at any

time. This provides a way to synchronize the counting cycle. A high level on a counter’s GATEn

signal enables counting; a low level on a counter’s GATEn signal disables counting.

Mode 2’s basic operation is outlined below and shown in Figure 10-8.

1. After a control word write, OUTn is driven high.

2. The count is loaded on the CLKINn pulse following one of these events:

• A write to a control word followed by a write to count

• A gate trigger

• The counter reaches one

3. On each succeeding CLKINn pulse, the count is decremented.

4. When the count reaches one, OUTn is driven low.

5. On the following CLKINn pulse, OUTn is driven high and the count is reloaded.

6. The process is repeated from step 3.

Writes to

Counter

n

CLKIN

n

GATE

n

OUT

n

?????0002 0001 0000 FFFF FFFE 0004

Control

Word = 12H

Count

Count = 4

0003

Count =2

A2397-02