13-25

SYNCHRONOUS SERIAL I/O UNIT

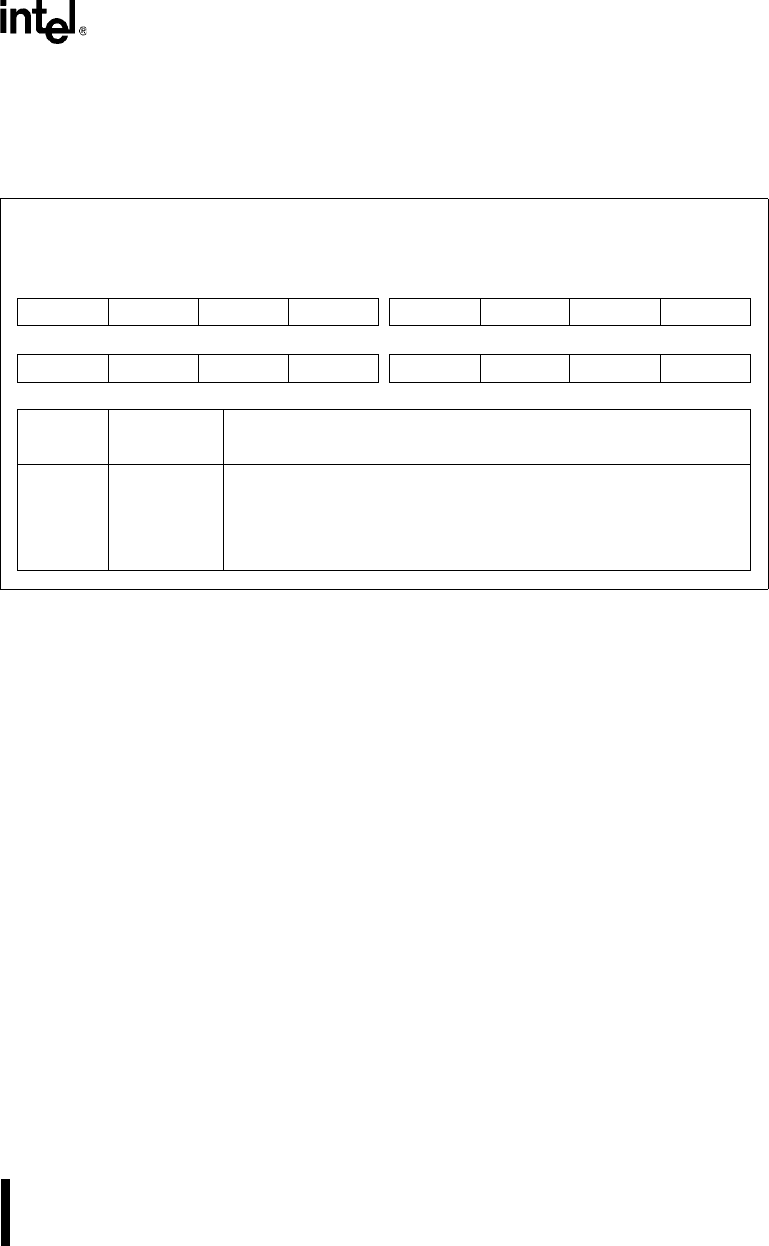

13.3.9 SSIO Receive Holding Buffer (SSIORBUF)

Read SSIORBUF to obtain the last data word received. Use the interrupt controller, DMA unit or

polling (read SSIOCON1) to determine when to read the receive buffer.

Figure 13-23. SSIO Receive Holding Buffer (SSIORBUF)

13.4 DESIGN CONSIDERATIONS

The transmit buffer empty signal can be connected to the interrupt control and DMA units. How-

ever, at high baud-rates interrupt latency is too long to prevent a transmit underrun error. For these

cases, use the DMA to load the data to be transmitted into the transmit buffer.

To illustrate this point, assume the maximum input transmit baud-rate of 8.25 MHz. To prevent a

transmit underrun error, a new 16-bit data word must be written to the transmit buffer before the

transmit shift register shifts out 16 bits.

At 33 MHz, one clock is 30 ns. The transmit buffer must be reloaded within 64 clocks (1939/30),

but interrupt latency is longer than 64 clocks. Therefore, the DMA unit is required to load the

transmit buffer.

Receive Holding Buffer

SSIORBUF

(read only)

Expanded Addr:

ISA Addr:

Reset State:

F482H

—

0000H

15 8

RB15 RB14 RB13 RB12 RB11 RB10 RB9 RB8

7 0

RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0

Bit

Number

Bit

Mnemonic

Function

15–0 RB15:0 Receive Buffer Bits:

This register contains the last word received. The receive shift register

shifts bits in with the rising edge of the receiver clock pin. Data is shifted

in starting with the most-significant bit. The control logic then transfers

the received word from the receive shift register to SSIORBUF.

16 bits

1

8.25 MHz

-------------------------

× 16 121 ns× 1939 ns==