Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

13-22

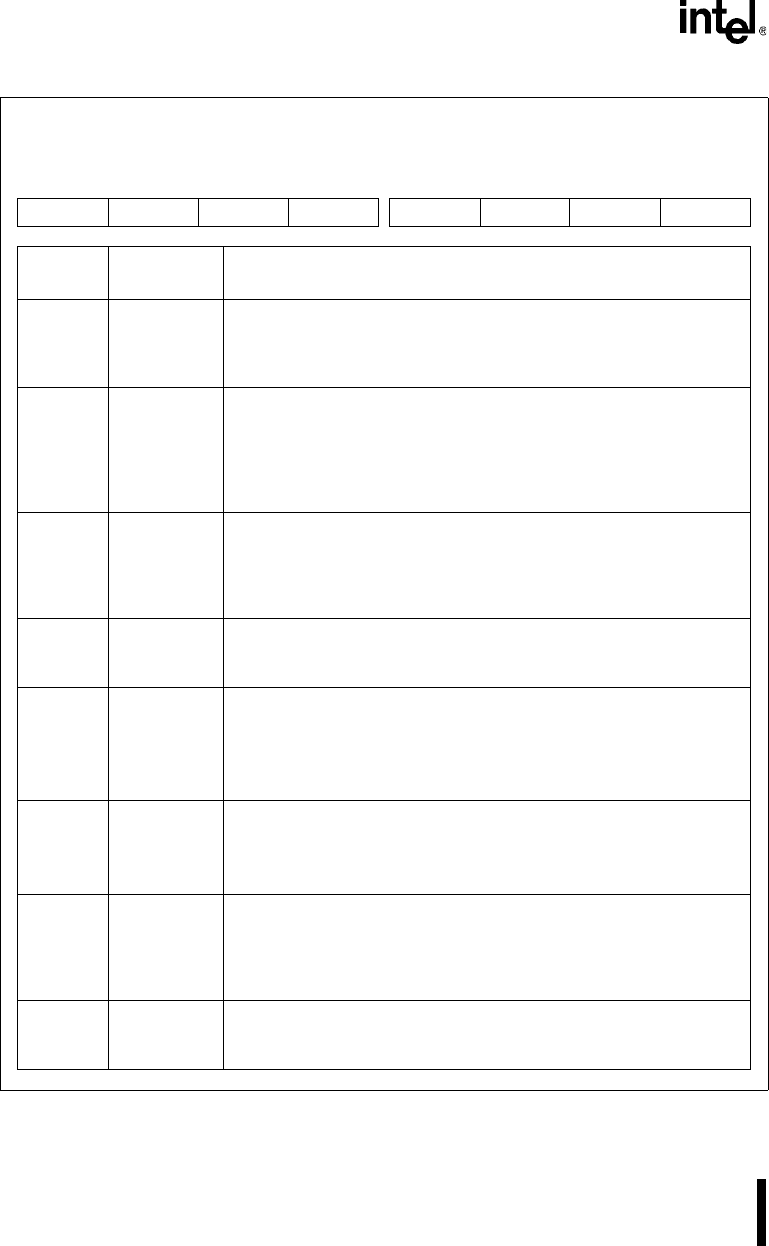

Figure 13-20. SSIO Control 1 Register (SSIOCON1)

SSIO Control 1

SSIOCON1

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F486H

—

C0H

7 0

TUE THBE TIE TEN ROE RHBF RIE REN

Bit

Number

Bit

Mnemonic

Function

7 TUE Transmit Underrun Error:

The transmitter sets this bit to indicate a transmit underrun error in the

TEN transfer mode. Clear this bit to clear the error flag. If a one is written

to TUE, it is ignored and TUE retains its previous value.

6 THBE

(read only bit)

Transmit Holding Buffer Empty:

The transmitter sets this bit when the transmit buffer contents have been

transferred to the transmit shift register, indicating that the buffer is now

ready to accept new data. Writing data to the transmit buffer clears

THBE. When this bit is clear, the buffer is not ready to accept any new

data.

5 TIE Transmitter Interrupt Enable:

0 = Clearing this bit prevents the Interrupt Control Unit from sensing

when the transmit buffer is empty.

1 = Setting this bit connects the transmit buffer empty internal signal to

the Interrupt Control Unit.

4 TEN Transmitter Enable:

0 = Disables the transmitter.

1 = Enables the transmitter.

3 ROE Receive Overflow Error:

The receiver sets this bit to indicate a receiver overflow error. Write zero

to this bit to clear the flag.

If a one is written to ROE, the one is ignored and ROE retains its

previous value.

2RHBF

(read only bit)

Receive Holding Buffer Full:

The receiver sets this bit when the receive shift register contents have

been transferred to the receive buffer.

Reading the buffer clears this bit.

1 RIE Receive Interrupt Enable:

0 = Clearing this bit prevents the Interrupt Control Unit from sensing

when the receive buffer is full.

1 = Setting this bit connects the receiver buffer full internal signal to the

Interrupt Control Unit.

0 REN Receiver Enable:

0 = Clearing this bit disables the receiver.

1 = Setting this bit enables the receiver.