Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

7-4

is no 64 Kbyte limit. The value loaded into the selector register is shifted to the left four bits and

moved into its corresponding descriptor base, then added to the effective address. The effective

address can be generated indirectly, using a 32-bit register. However, only 16 bits of the Extended

Instruction Pointer (EIP) register are pushed onto the stack during calls, exceptions and INTR ser-

vices. Therefore, when returning from calls, exceptions or INTRs, the upper 16 bits of the 32-bit

EIP are zero. In an SMI# handler, the EIP should not be over the 64 Kbyte boundary. The 16-bit

CS allows addressing within a 1 Mbyte boundary.

Instructions that explicitly access the stack, such as MOV instructions, can access the entire

4 Gbytes of logical address space by using a 32-bit address size prefix. However, instructions that

implicitly access the stack, such as POP, PUSH, CALL, and RET, still have the 64 Kbytes limit.

After SMI# is recognized and the processor state is saved, the processor state is initialized to the

default values shown in Table 7-2.

When a valid SMI# is recognized on an instruction execution boundary, the CPU immediately

begins execution of the SMM State Save sequence, asserting SMIACT# low (unless the CPU is

in a shutdown condition). The CPU then starts SMI# handler execution. An SMI# cannot inter-

rupt a CPU shutdown. The SMI# handler always starts at 38000H. When there are multiple causes

of SMI#s, only one SMI# is generated, thereby ensuring that SMI#s are not nested.

7.3.2 System Management Interrupt

The Intel386 EX processor extends the standard Intel386 microprocessor architecture by adding

a new feature called the system management interrupt (SMI#). This section describes in detail

how the system designer uses SMI#.

The execution unit recognizes an SMI# (falling edge) on an instruction boundary (see instruction

#3 in Figure 7-1). After all CPU bus cycles have completed, including pipelined cycles, the state

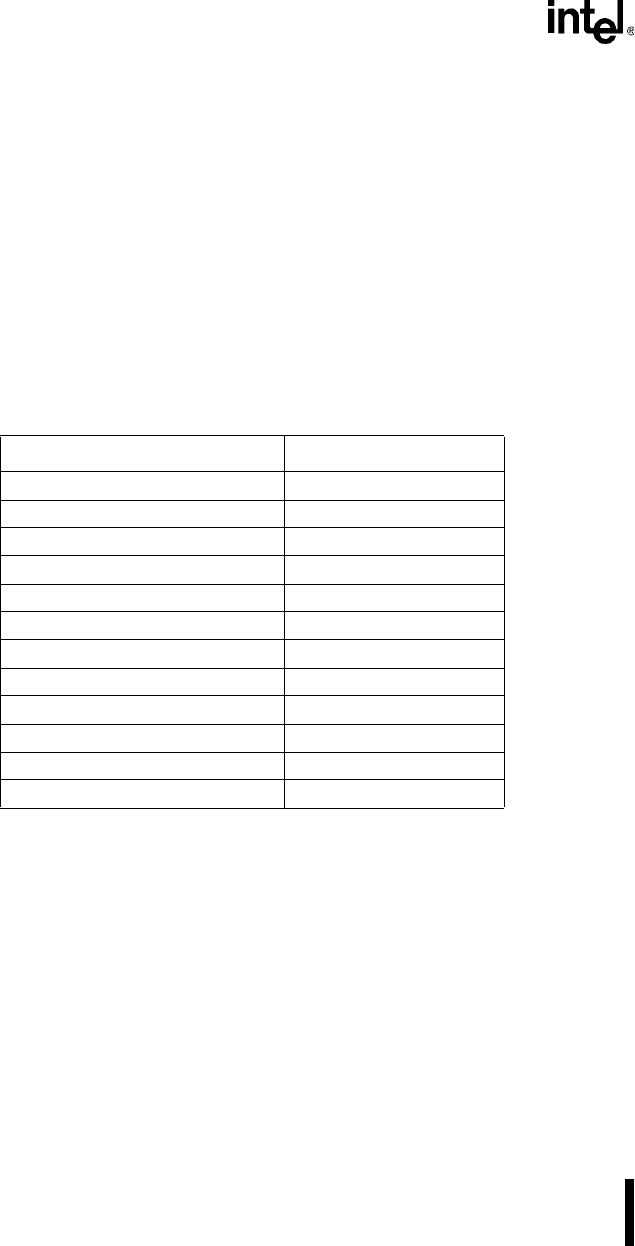

Table 7-2. SMM Processor State Initialization Values

Register Content

General Purpose Register Unpredictable

EFLAGS 00000002H

EIP 00008000H

CS Selector 3000H

DS,ES,FS,GS,SS Selectors 0000H

CS Descriptor Base 00030000H

DS,ES,FS,GS,SS Descriptor Base 00000000H

CS,DS,ES,FS,GS,SS Descriptor Limit 0FFFFFH

DS,ES,FS,GS,SS Attributes 16-bit

CR0 Bits 0, 1, 2, 3, 31 cleared

DR6 Unpredictable

DR7 Bits 0–10,16–31 cleared