Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

12-26

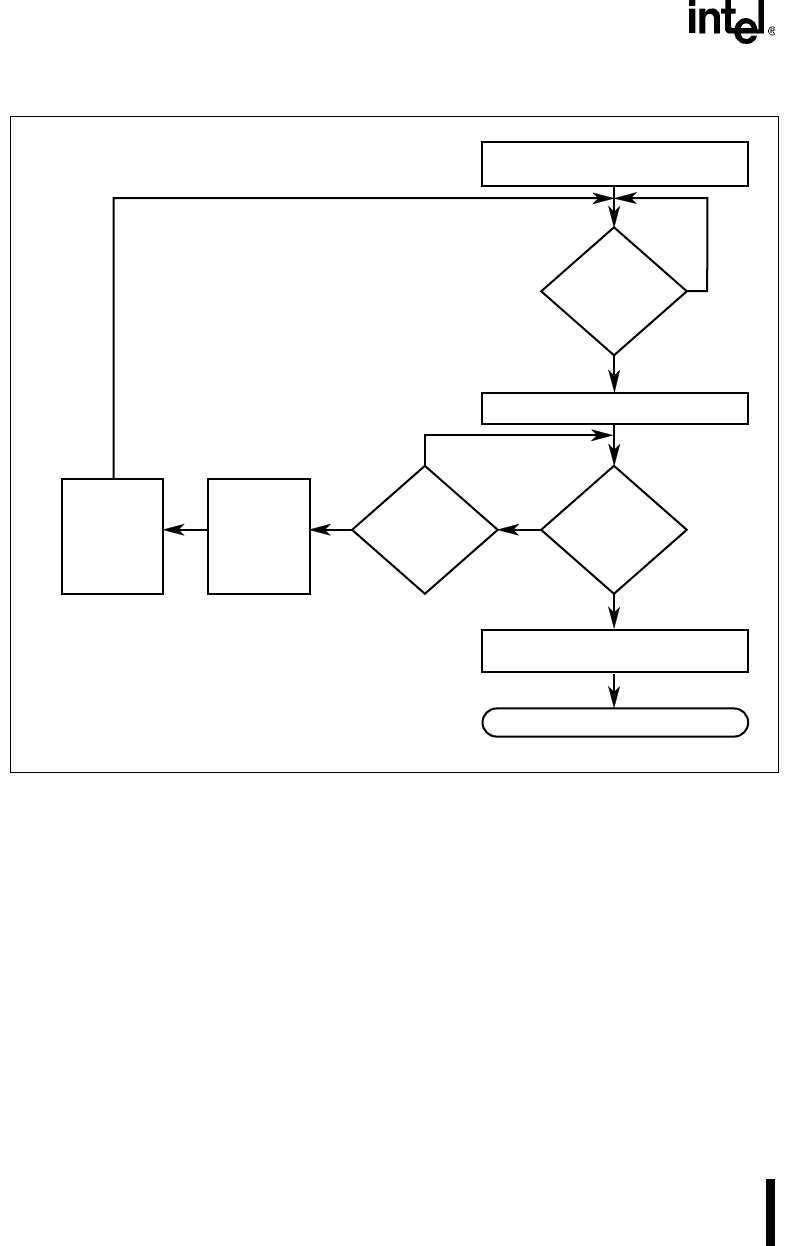

Figure 12-17. Cascade Mode

12.2.9 DMA Interrupts

Each channel contains two interrupt causing signals, chaining status and transfer complete. When

a channel is configured for the chaining buffer-transfer mode, the chaining status signal indicates

that the channel has started its buffer transfer and new transfer information can be written without

affecting the current buffer transfer. Once activated, the chaining status signal remains active until

the most significant byte of the base target address is written, or resetting the chaining enable bit.

The transfer complete status signal indicates that the channel has finished a buffer transfer —

either the channel’s byte count has expired or the buffer transfer was terminated by an EOP#

input. DMACLRTC clears the DMAINT signal going to the Interrupt Control Unit. DMACLRTC

is executed by writing to location F01EH; the data written to the location is immaterial — writing

any data to the location causes the DMA to deactivate the transfer complete status signal.

Cascade cycle complete.

A2337-02

DRQ

n

active?

Yes

No

Refresh

request?

Yes

No

Cascaded

device

deasserts

DRQ

n

,

relinquishing

bus control.

Refresh

cycle is

performed.

DRQ

n

active?

Yes

No

After initialization, the DMA channel

is programmed.

Cascaded device gains bus control.

Cascaded device relinquishes bus

control.