Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

6-20

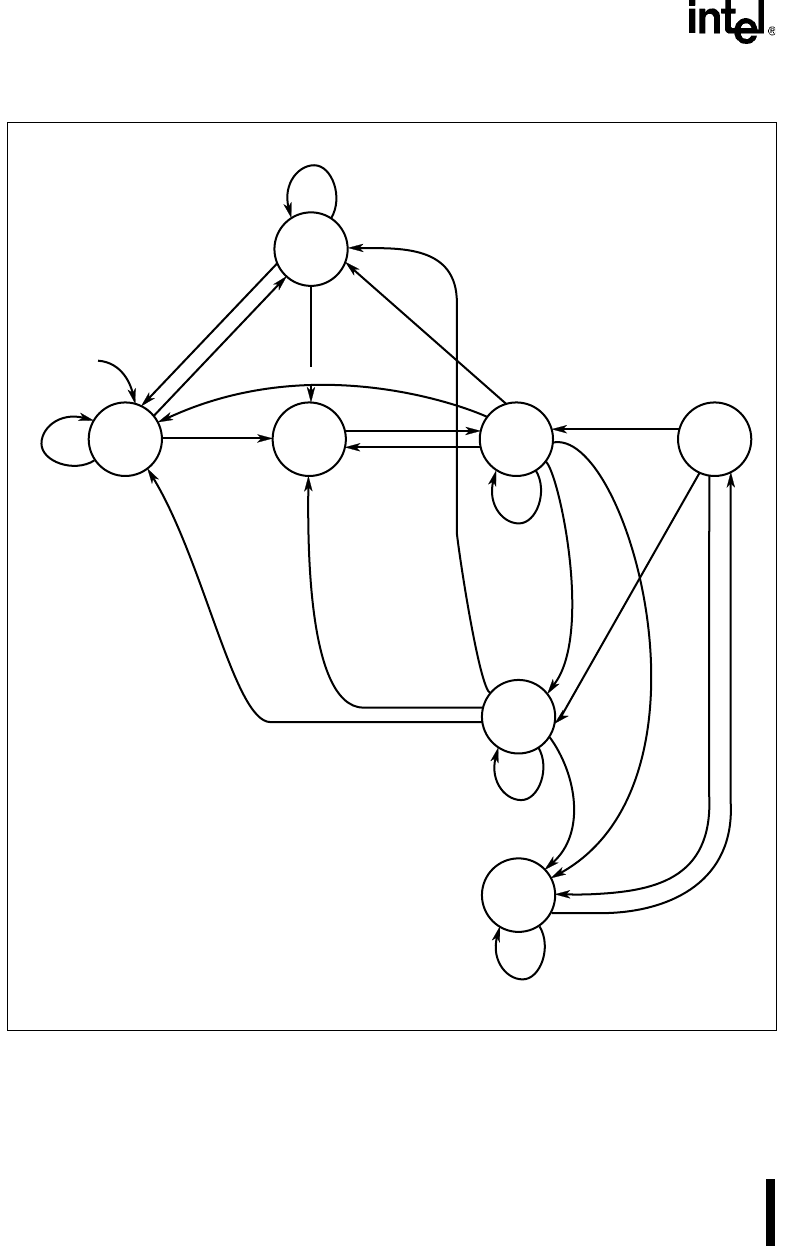

Figure 6-7. Complete Bus States (Including Pipelined Address)

A2376-02

HOLD Asserted

READY# Asserted •

HOLD Asserted

HOLD Negated •

Request Pending

READY# Asserted •

HOLD Asserted

HOLD Negated •

No Request

Reset

Asserted

HOLD Negated •

No Request

HOLD Asserted

READY# Negated •

NA# Negated

READY# Asserted •

HOLD Negated •

Request Pending

Always

NA# Negated

READY# Asserted •

HOLD Negated •

Request Pending

NA# Asserted •

(HOLD Asserted

+ No Request)

Request Pending •

HOLD Negated

READY# Asserted •

HOLD Negated •

No Request

(No Request + HOLD Asserted) •

NA# Asserted •

READY# Negated

READY# Negated •

(No Request +

HOLD Asserted)

READY# Negated

READY# Negated •

NA# Asserted •

HOLD Negated •

Request Pending

READY# Negated •

Request Pending •

HOLD Negated

READY# Asserted

T2P

T2i

T2

T1P

T1Ti

Th

Bus States:

T1—first clock of a non-pipelined bus cycle.

T2—subsequent clock of a bus cycle when NA# has

not been sampled active in the current bus cycle.

T2i—subsequent clocks of a bus cycle when NA# has

been sampled active in the current bus cycle and there

is not yet an internal bus request pending.

T2P—subsequent clocks of a bus cycle when NA# has

been sampled active in the current bus cycle and there

is an internal bus request pending.

T1P—first clock of a pipelined bus cycle.

Ti—idle state.

Th—hold acknowledge state.

R

E

A

D

Y

#

A

s

s

e

r

t

e

d

•

H

O

L

D

N

e

g

a

t

e

d

•

N

o

R

e

q

u

e

s

t

NA# Asserted •

HOLD Negated •

Request Pending