Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

D-22

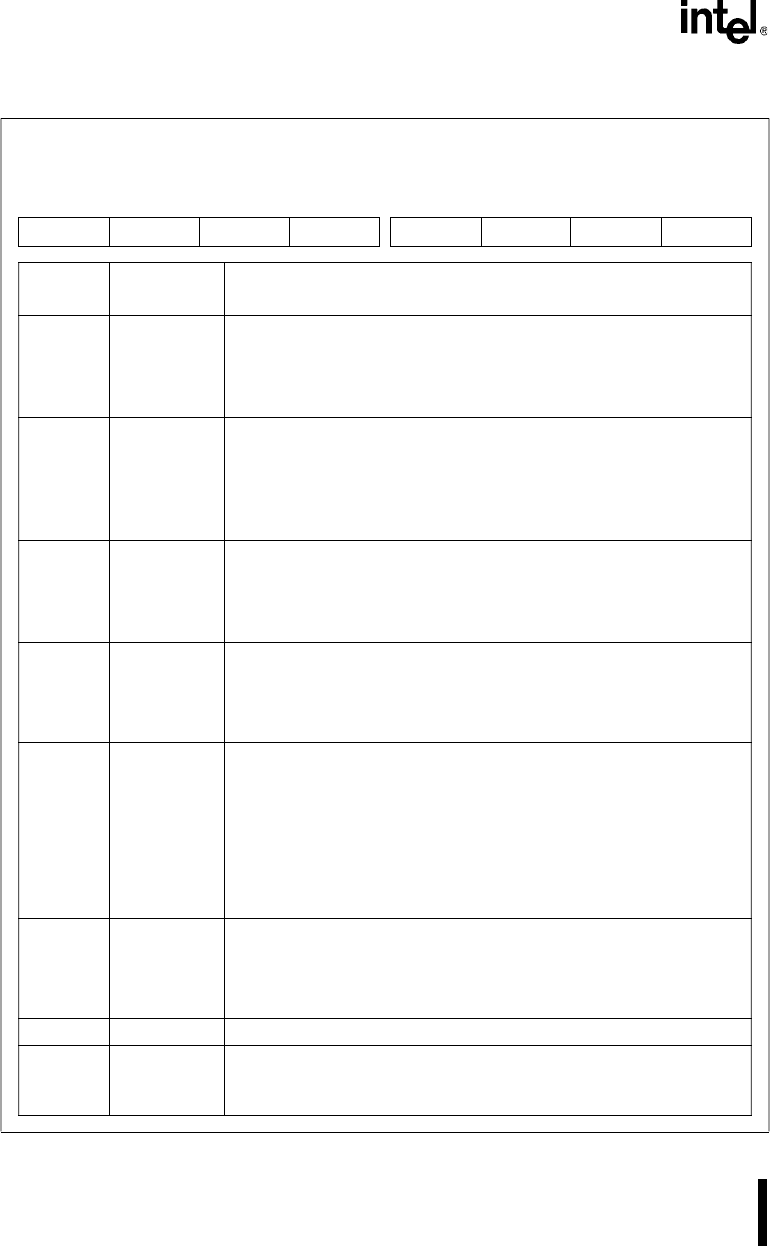

D.17 DMAMOD2

DMA Mode 2

DMAMOD2

(write only)

Expanded Addr:

ISA Addr:

Reset State:

F01BH

—

00H

7 0

BCO RD TD RH RI TH 0 CS

Bit

Number

Bit

Mnemonic

Function

7 BCO Bus Cycle Option:

0 = Selects the fly-by data transfer bus cycle option for the channel specified

by bit 0.

1 = Selects the two-cycle data transfer bus cycle option for the channel

specified by bit 0.

6 RD Requester Device Type:

0 = Clear this bit when the requester for the channel specified by bit 0 is in

memory space.

1 = Set this bit when the requester for the channel specified by bit 0 is in I/O

space.

This bit is ignored if BCO is cleared.

5 TD Target Device Type:

0 = Clear this bit when the target for the channel specified by bit 0 is in

memory space.

1 = Set this bit when the target for the channel specified by bit 0 is in I/O

space.

4 RH Requester Address Hold:

0 = Causes the address to be modified (incremented or decremented,

depending on DMAMOD2.3).

1 = Causes the requester’s address for the channel specified by bit 0 to

remain constant during a buffer transfer.

3 RI Requester Address Increment/Decrement:

0 = Causes the requester address to be incremented after each data transfer

in a buffer transfer.

1 = Causes the requester address for the channel specified by bit 0 to be

decremented after each data transfer in a buffer transfer. Note that it

does not decrement words. When decrementing it will do two byte

transfers for a word.

Note: When the target address is programmed to remain constant

(DMAMOD2.4 = 1), this bit is a don’t care.

2 TH Target Address Hold:

0 = Causes the address to be modified (incremented or decremented,

depending on DMAMOD1.5).

1 = Causes the target’s address for the channel specified by bit 0 to remain

constant during a buffer transfer.

1 0 Must be 0 for correct operation.

0 CS Channel Select:

0 = The selections for bits 7–2 affect channel 0.

1 = The selections for bits 7–2 affect channel 1.