12-21

DMA CONTROLLER

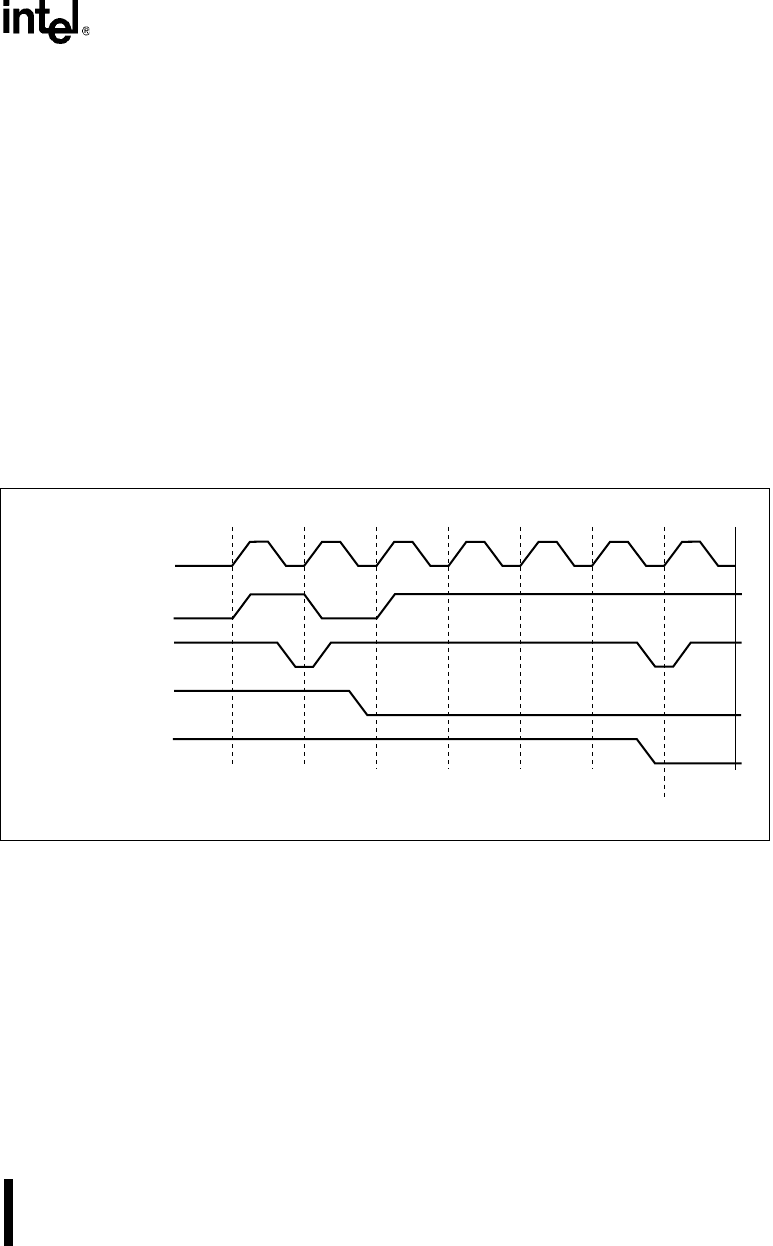

12.2.7.3 Demand Data-transfer Mode

In demand data-transfer mode, a channel request initiates a buffer transfer. The channel gains bus

control and begins the buffer transfer. As long as the request signal (DRQn) remains active, the

channel continues to perform data transfers. When the DRQn signal goes inactive, the channel

completes its current bus cycle and relinquishes bus control, suspending the buffer transfer. In this

way, the demand mode allows peripherals to access memory in small, irregular bursts without

wasting bus control time. As in other data-transfer modes, a buffer transfer is completed when the

buffer’s byte count expires or is terminated if the EOP# input is activated. At this point, the chan-

nel’s buffer-transfer mode determines whether the channel becomes idle or is reprogrammed.

Since DRQn going inactive suspends a buffer transfer, the channel continually samples DRQn

during a demand buffer transfer. During a buffer transfer, the channel can sample DRQn synchro-

nously or asynchronously (it always samples DRQn asynchronously at the start of a buffer trans-

fer). With synchronous sampling, the channel samples DRQn at the end of the last state of every

data transfer. With asynchronous sampling, the channel samples DRQn at the beginning of every

state, then waits until the end of the state to act on the input. See Figure 12-13. The DRQn sam-

pling is programmed in the DMACMD2 register (Figure 12-24).

Figure 12-13. Buffer Transfer Suspended by the Deactivation of DRQ

n

The demand data-transfer mode is compatible with all of the buffer-transfer modes. The follow-

ing flowcharts show the transfer process flow for a channel programmed for the demand data-

transfer mode with each buffer-transfer mode: single (Figure 12-14), autoinitialize (Figure

12-15), and chaining (Figure 12-16).

A2481-02

CLKOUT

ADS#

READY#

DRQ

n

(Async)

DRQ

n

(Sync)

T2 T2T2 T2T1 TiT2

DMA Cycle

x

Cycle