Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

7-10

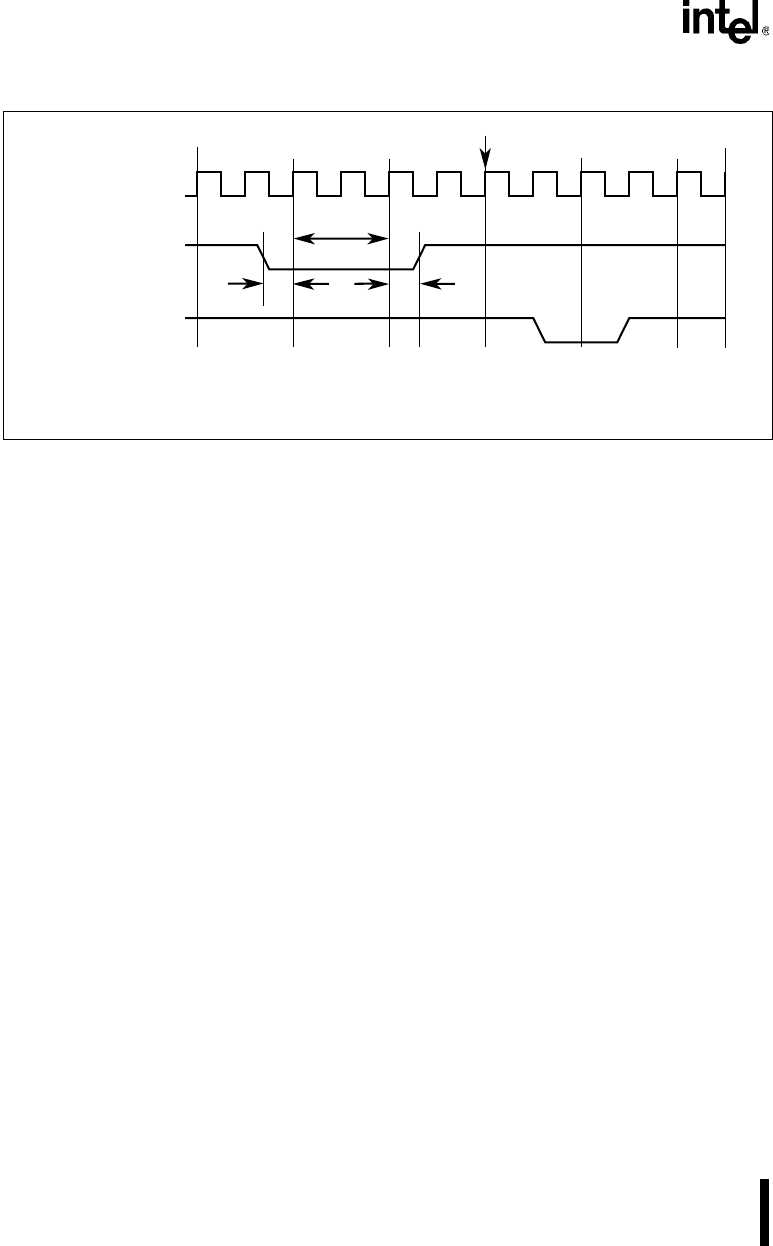

Figure 7-5. SMI# Timing

7.3.2.5 I/O Restart

Bit 16 of the SMM Revision Identifier is set (1) indicating that this device does support the I/O

trap restart extension to the SMM base architecture.

The I/O trap restart slot provides the SMM handler the option of automatically re-executing an

interrupted I/O instruction using the RSM instruction. When the RSM instruction is executed

with the I/O trap restart slot set to a value of 0FFH, the CPU automatically re-executes the I/O

instruction that the SMI# has trapped. If the slot contains 00H when the RSM instruction is exe-

cuted, the CPU does not re-execute the I/O instruction. This slot is initialized to 00H during an

SMI#. It is the SMM handler’s responsibility to load the I/O trap restart slot with 0FFH when re-

start is desired.

NOTE

The SMM handler must not set the I/O trap restart slot to 0FFH when the

SMI# is not asserted on an I/O instruction boundary, because this causes

unpredictable results.

7.3.3 SMM Handler Interruption

7.3.3.1 Interrupt During SMM Handler

When the CPU enters SMM, both INTR and NMI are disabled (Figure 7-6). The SMM handler

may enable INTR by executing the STI instruction. NMI is enabled after the completion of the

first interrupt service routine (software or hardware initiated ISR) or exception handler within the

SMM handler. Software interrupt and exception instructions are not blocked during the SMM

handler.

The SMM feature can be used without any other interrupts. INTR and NMI are blocked by the

system during SMI#, unless enabled by software. If INTR or NMI are not enabled during SMM,

A2511-02

CLK2

Priority Arbitration

SMI#

Sampled

T

su

T

hold

SMI#

RDY#

T

su

= SMI# setup time, T

hold

= SMI# hold time