D-5

SYSTEM REGISTER QUICK REFERENCE

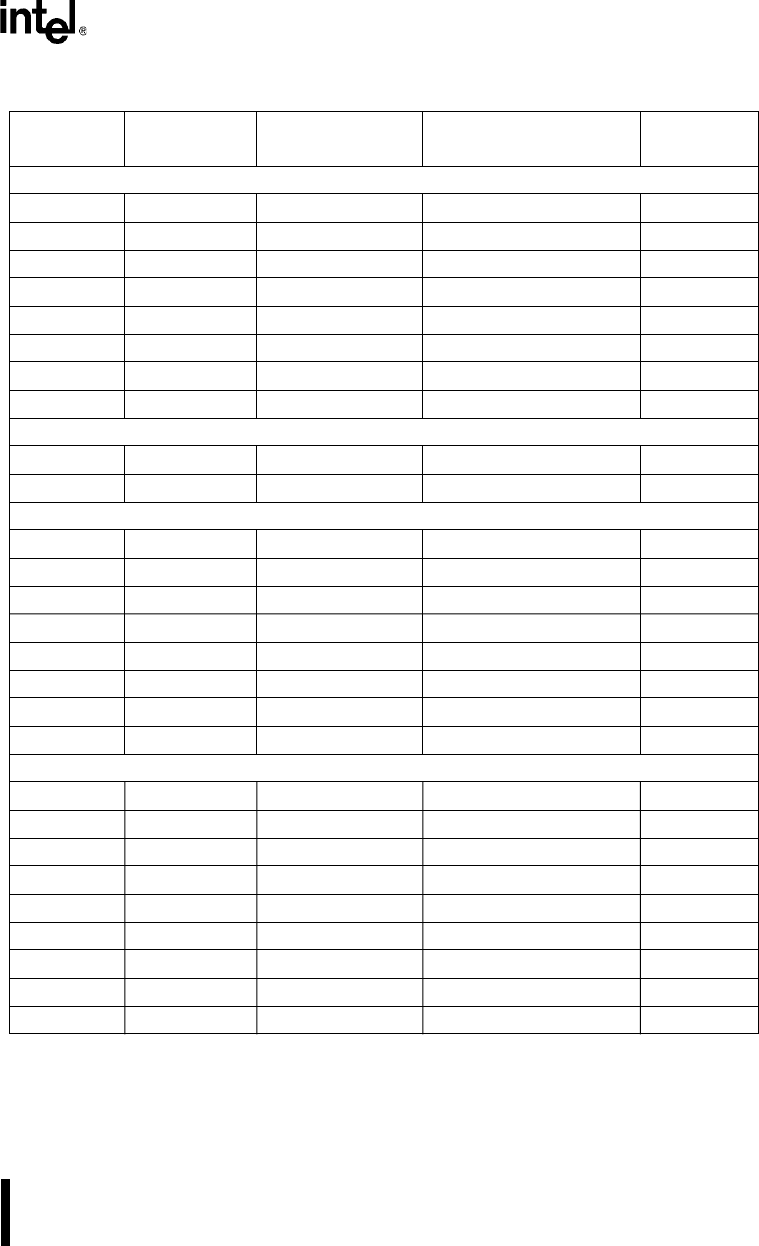

Asynchronous Serial I/O Channel 0 (COM1)

F4F8H 03F8H Byte RBR0/TBR0/DLL0 XX/XX/02H

F4F9H 03F9H Byte IER0/DLH0 00H/00H

F4FAH 03FAH Byte IIR0 01H

F4FBH 03FBH Byte LCR0 00H

F4FCH 03FCH Byte MCR0 00H

F4FDH 03FDH Byte LSR0 60H

F4FEH 03FEH Byte MSR0 X0H

F4FFH 03FFH Byte SCR0 XX

Clock Generation and Power Management

F800H Byte PWRCON 00H

F804H Word CLKPRS 0000H

Device Configuration Registers

F820H Byte P1CFG 00H

F822H Byte P2CFG 00H

F824H Byte P3CFG 00H

F826H Byte PINCFG 00H

F830H Byte DMACFG 00H

F832H Byte INTCFG 00H

F834H Byte TMRCFG 00H

F836H Byte SIOCFG 00H

Parallel I/O Ports

F860H Byte P1PIN XX

F862H Byte P1LTC FFH

F864H Byte P1DIR FFH

F868H Byte P2PIN XX

F86AH Byte P2LTC FFH

F86CH Byte P2DIR FFH

F870H Byte P3PIN XX

F872H Byte P3LTC FFH

F874H Byte P3DIR FFH

Table D-1. Peripheral Register Addresses (Sheet 5 of 6)

Expanded

Address

PC/AT

Address

Access Type

(Byte/Word)

Register Name Reset Value

NOTES:

1. Byte pointer in flip-flop in DMA determines which register is accessed.

2. Shaded rows indicate reserved areas.