Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

14-20

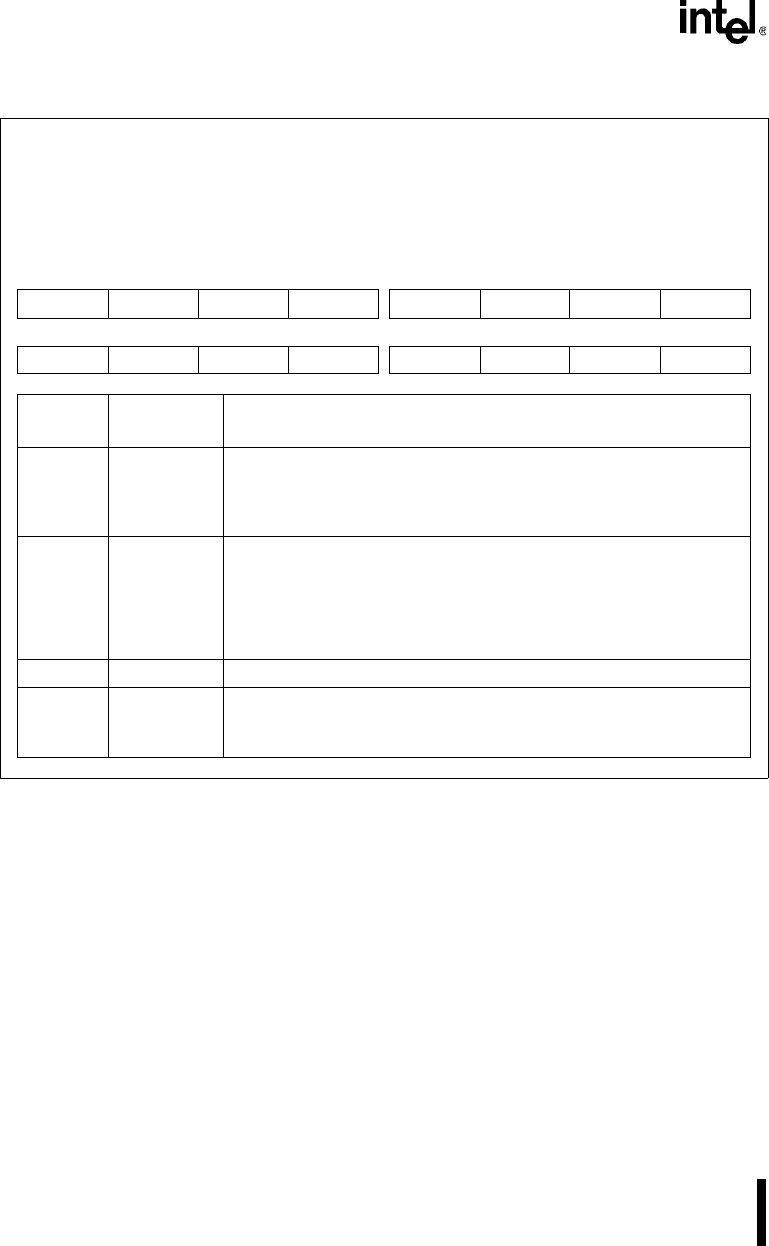

Figure 14-9. Chip-select Low Mask Registers (CS

n

MSKL, UCSMSKL)

Chip-select Low Mask

CS

n

MSKL (

n

= 0–6), UCSMSKL

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F404H, F40CH

F414H, F41CH

F424H, F42CH

F434H, F43CH

—

0000H (CS

n

MSKL)

FFFFH (UCSMSKL)

15 8

CM5 CM4 CM3 CM2 CM1 CMSMM — —

7 0

———— ———CSEN

Bit

Number

Bit

Mnemonic

Function

15–11 CM5:1 Chip-select Mask Value Lower Bits:

Defines the lower 5 bits of the channel’s 15-bit mask. The mask bits

CM5:1 and the address bits CA5:1 form a masked address that is

compared to memory address bits A15:11 or I/O address bits A5:1.

10 CMSMM SMM Mask Bit:

0 = The SMM address bit is not masked.

1 = Masks the SMM address bit in the channel’s Chip-Select Low

Address register. When the SMM address bit is masked, an address

match activates the chip-select, regardless of whether the processor

is in SMM.

9–1 — Reserved; for compatibility with future devices, write zeros to these bits.

0 CSEN Chip-select Enable:

0 = Disables the chip-select channel.

1 = Enables the chip-select channel.