Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

A-4

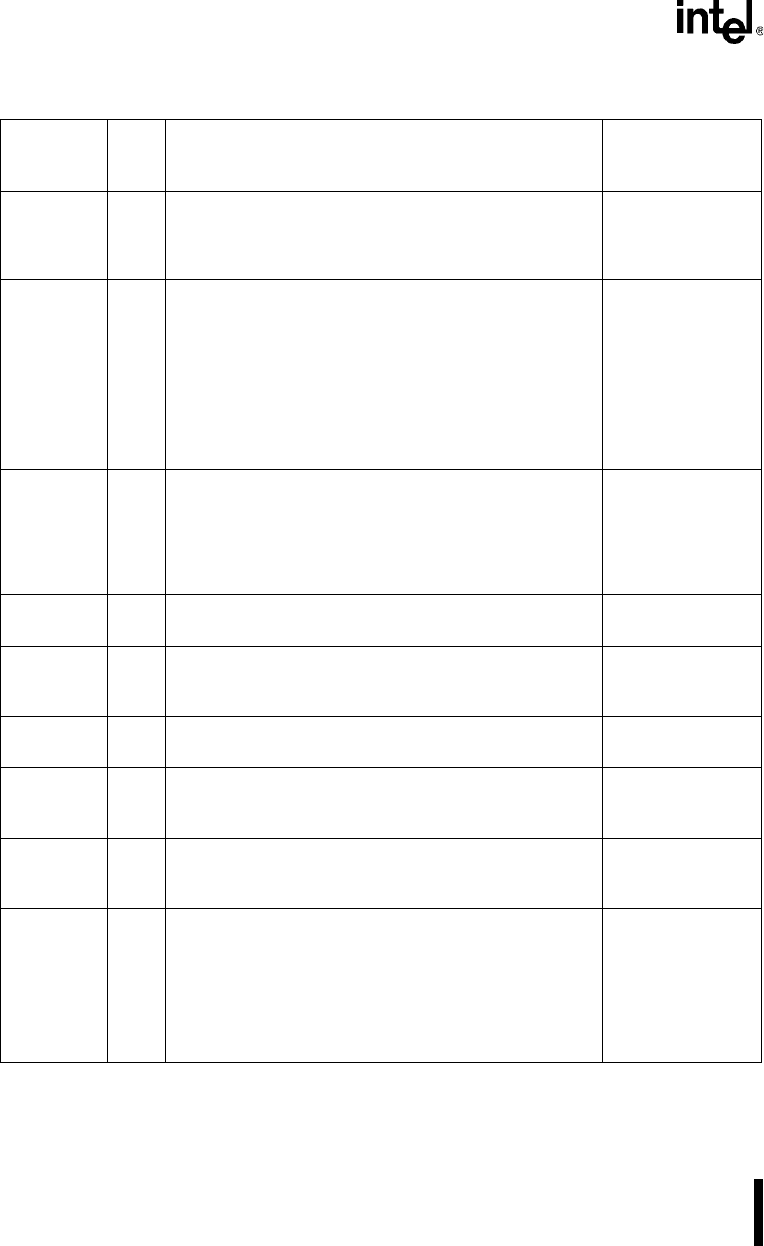

HOLD I Hold Request:

An external bus master asserts HOLD to request control of

the local bus. The processor finishes the current nonlocked

bus transfer, releases the bus signals, and asserts HLDA.

P1.6

INT9

INT8

INT7

INT6

INT5

INT4

INT3

INT2

INT1

INT0

I Interrupt Requests:

These maskable inputs cause the processor to suspend

execution of the current program and execute an interrupt

acknowledge cycle.

P3.0/TMROUT0

P3.1/TMROUT1

TMRGATE1

TMRCLK1

TMRGATE0

TMRCLK0

P3.5

P3.4

P3.3

P3.2

LBA# O Local Bus Access:

Indicates that the processor provides the READY# signal

internally to terminate a bus transaction. This signal is

active when the processor accesses an internal peripheral

or when the chip-select unit provides the READY# signal for

an external peripheral.

—

LOCK# O Bus Lock:

Prevents other bus masters from gaining control of the bus.

P1.5

M/IO# O Memory/IO:

Indicates whether the current bus cycle is a memory cycle

or an I/O cycle.

—

NA# I Next Address:

Requests address pipelining.

—

NMI ST Nonmaskable Interrupt Request:

Causes the processor to suspend execution of the current

program and execute an interrupt acknowledge cycle.

—

PEREQ I Processor Extension Request:

Indicates that the math coprocessor has data to transfer to

the processor.

TMRCLK2

P1.7

P1.6

P1.5

P1.4

P1.3

P1.2

P1.1

P1.0

I/O Port 1:

General-purpose, bidirectional I/O port.

HLDA

HOLD

LOCK#

RI0#

DSR0#

DTR0#

RTS0#

DCD0#

Table A-2. Description of Signals Available at the Device Pins (Sheet 3 of 6)

Signal Type Name and Description

Multiplexed With

(Alternate

Function)