Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

5-18

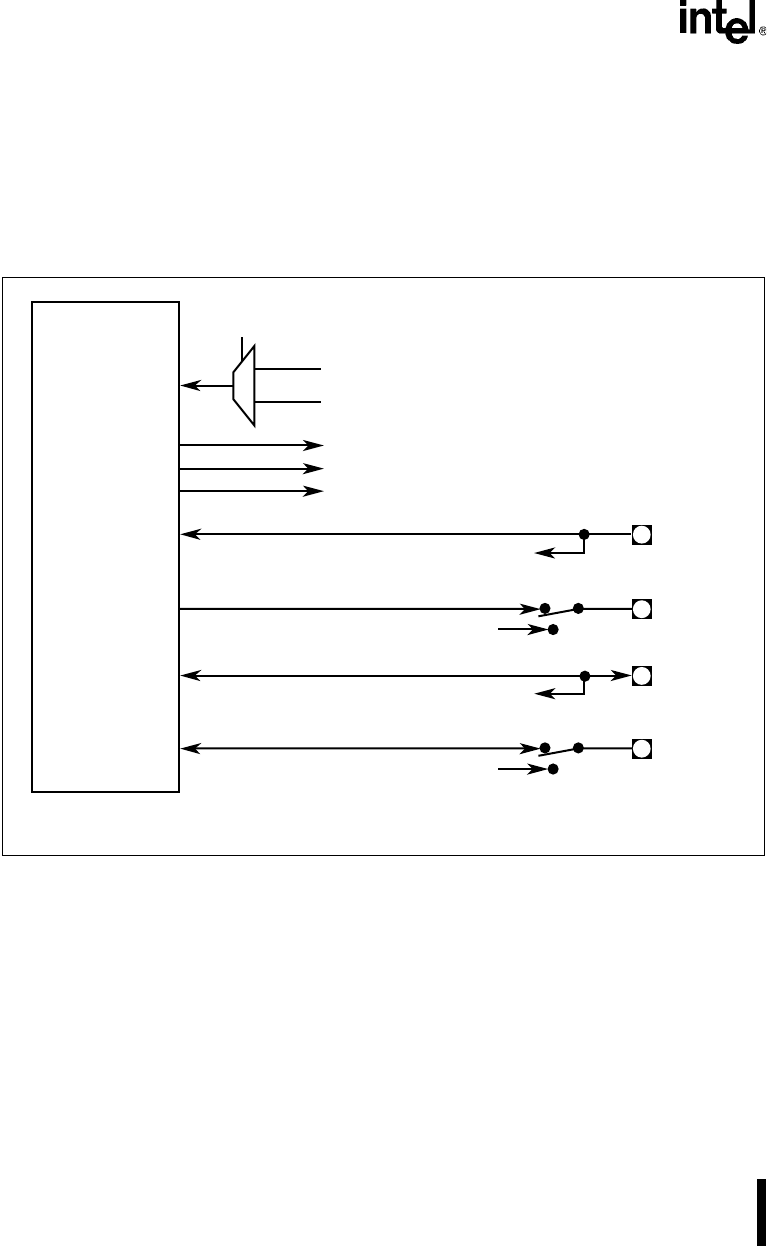

5.2.5 Synchronous Serial I/O Configuration

The synchronous serial I/O unit (SSIO) is shown in Figure 5-11. Its single configuration register

bit is in the SIOCFG register (Figure 5-10). The transmit buffer empty and receive buffer full sig-

nals (SSTBE and SSRBF) go to the DMA unit (Figure 5-2), and an interrupt signal (SSIOINT)

goes to the ICU (Figure 5-4). Depending on the settings in the SSIOCON1 register (see Chapter

13), SSIOINT is asserted for one of two conditions: the receive buffer is full or the transmit buffer

is empty. Note that using the SSIO signals precludes the use of four of the SIO1 modem signals.

Figure 5-11. SSIO Unit Configuration

A2518-02

Receive Data

Transmit Data

Transmit Clock

SSIO

Receive Clock

0

1

SSIOTX

(RTS1#)

From SIO1

PINCFG.0

PSCLK

SIOCFG.2

SSIORX

(RI1#)*

To SIO1

*Alternate pin signals are in parentheses.

SERCLK

BCLKIN

STXCLK

(DSR1#)

To SIO1

SRXCLK

(DTR1#)

From SSIO1

PINCFG.1

To ICU

To DMA

To DMA

SSIOINT

SSRBF

SSTBE

0

1

0

1