Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

12-2

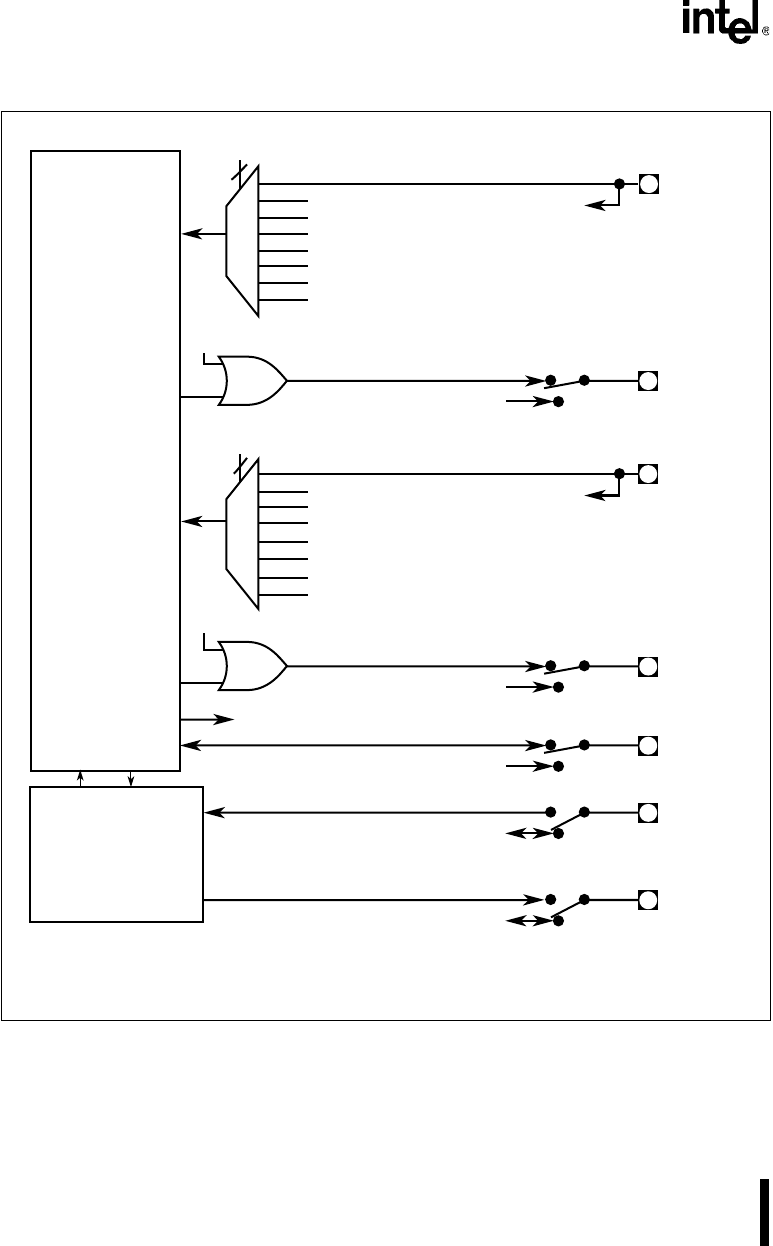

Figure 12-1. DMA Unit Block Diagram

A2531-02

DREQ0

DMAACK0#

DREQ1

DMAACK1#

DMAINT

DMA

Bus Arbiter

HOLD

HLDA

RBFDMA1 (SIO1 )

TXEDMA0 (SIO0)

SSRBF (SSIO)

DRQ0

(DCD1#)†

To SIO1

DRQ1

(RXD1)

To SIO1

DACK0#

(CS5#)

DMACFG.3

From CSU

DACK1#

(TXD1)

DMACFG.7

From SIO1

DMACFG.6:4

3

DMACFG.2:0

PINCFG.4

PINCFG.2

EOP#

(CTS1#)

From SIO1

PINCFG.3

HOLD

(P1.6)

To/From I/O Port 1

P1CFG.6

HLDA

(P1.7)

To/From I/O Port 1

P1CFG.7

3

† Alternate pin signals are in parentheses.

End of Process

OUT2 (TCU)

RBFDMA0 (SIO0)

TXEDMA1 (SIO1)

SSTBE (SSIO)

0

1

2

3

4

5

6

7

RBFDMA0 (SIO0)

TXEDMA1 (SIO1)

SSTBE (SSIO)

OUT1 (TCU)

RBFDMA1 (SIO1)

TXEDMA0 (SIO0)

SSRBF (SSIO)

0

1

2

3

4

5

6

7

1

0

1

0

1

0

0

1

1

0

To ICU