12-47

DMA CONTROLLER

12.3.13 Chaining Register (DMACHR)

Use DMACHR to enable or disable the chaining buffer-transfer mode for a selected channel. The

following steps describe how to set up a channel to perform chaining buffer transfers.

1. Set up the chaining interrupt (DMAINT) service routine.

2. Configure the channel for the single buffer-transfer mode.

3. Program the mode registers.

4. Program the target address, requester address, and byte count registers.

5. Enable the channel for the chaining buffer-transfer mode. (This enables the DMAINT

output.)

6. Enable the DMAINT interrupt in the ICU and service it. (The service routine should load

the transfer information for the next buffer transfer.)

7. Enable the channel by unmasking DREQn and setting bit 2 in DMACMD1.

From this point, the chaining interrupt indicates each time the channel requires new transfer in-

formation. The cycle continues as long as the chaining buffer-transfer mode is enabled and new

transfer information is written to the channel. New transfer information must be written to the

channel before the channel’s current buffer transfer completes.

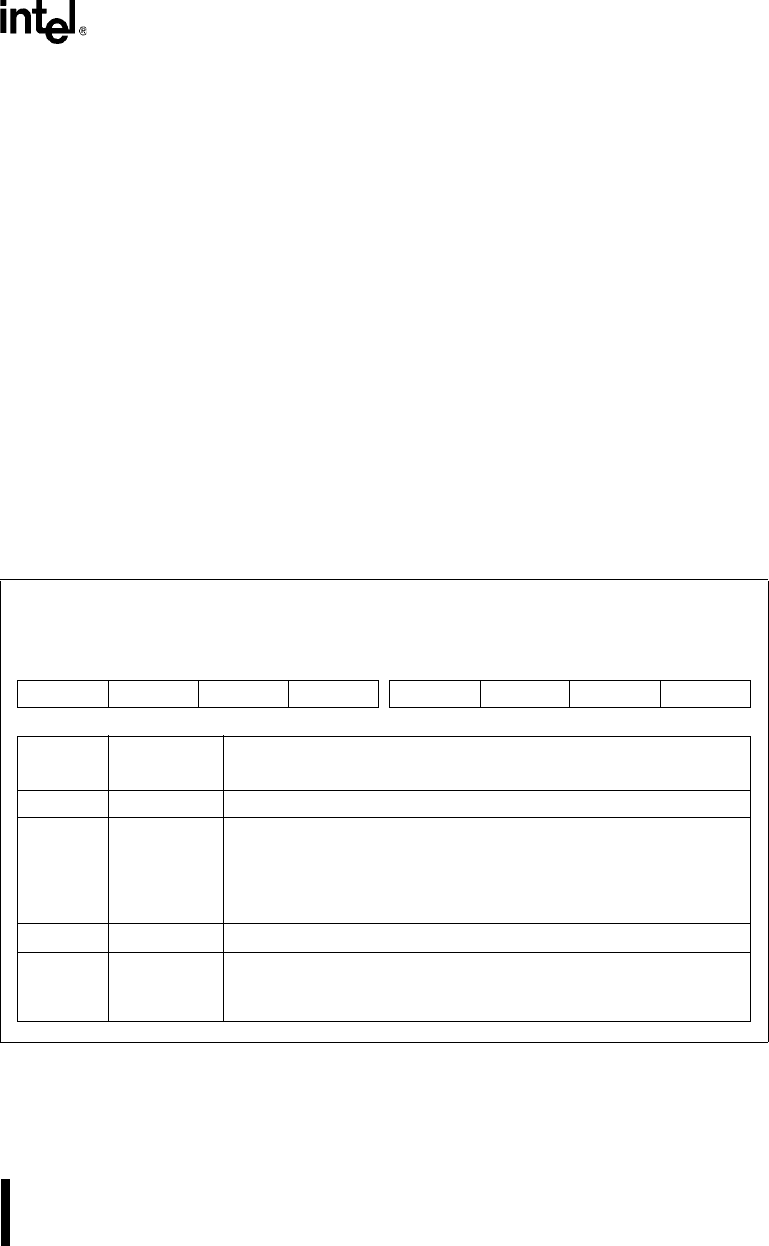

Figure 12-32. DMA Chaining Register (DMACHR)

DMA Chaining

DMACHR

(write only)

Expanded Addr:

ISA Addr:

Reset State:

F019H

—

00H

7 0

———— —CE0CS

Bit

Number

Bit

Mnemonic

Function

7–3 — Reserved; for compatibility with future devices, write zeros to these bits.

2 CE Chaining Enable:

0 = Disables the chaining buffer-transfer mode for the channel specified

by bit 0.

1 = Enables the chaining buffer-transfer mode for the channel specified

by bit 0.

1 0 Must be 0 for correct operation.

0 CS Channel Select:

0 = The selection for bit 2 affects channel 0.

1 = The selection for bit 2 affects channel 1.