7-9

SYSTEM MANAGEMENT MODE

7.3.2.3 HALT Restart

It is possible for SMI# to break into the HALT state. In some cases the application might want to

return to the HALT state after RSM. The SMM architecture provides the option of restarting the

HALT instruction after RSM.

The word at address 03FF02H is the HALT restart slot. The processor sets bit 0 of this location

when the processor is in the HALT state while the SMI# occurred. If the SMM driver leaves this

bit set, then the processor re-enters the HALT state when it exits from SMM. When the driver

clears this bit, the processor continues execution with the instruction just after the interrupted

HALT instruction.

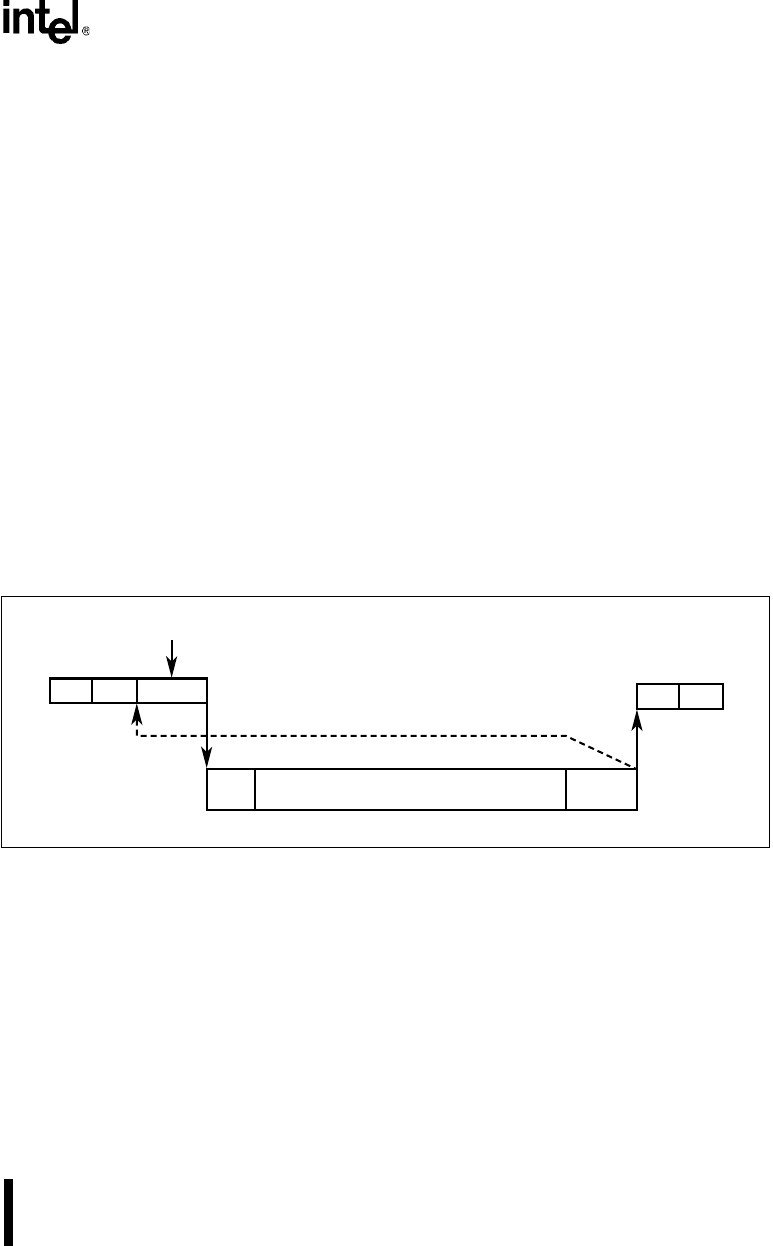

7.3.2.4 System Management Interrupt During I/O Instruction

Like the HALT restart feature, the processor allows restarting I/O cycles which have been inter-

rupted by an SMI#. This gives the system designer the option of performing a hardware I/O cycle

restart without having to modify either application, operating system, or BIOS software. (See Fig-

ure 7-4.)

When a SMI# occurs during an I/O cycle, it then becomes the responsibility of the SMM handler

to determine the source of the SMI#. If, for example, the source is the powered down I/O device,

the SMM handler would power up the I/O device and reinitialize it. The SMM handler would then

write 0FFH to the I/O restart slot in the SMM State Dump area and the RSM instruction would

then restart the I/O instruction.

Figure 7-4. SMI# During I/O Instruction

The SMI# input signal can be asynchronous; as a result, SMI# must be valid at least three clock

periods before READY# is asserted for it to be recognized right after the current bus cycle. SMI#

must be sampled valid for at least two clocks, with the other clock used to internally arbitrate for

control. See Figure 7-5 for details. (Note that this diagram is only for I/O cycles and memory data

read cycles.)

A2509-01

State

Save

SMI#

SMM

Handler

Instr

State

Resume

Instr Instr

#1 #2

#4 #5

I/O Instr

Instr

#3

Option