Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

7-14

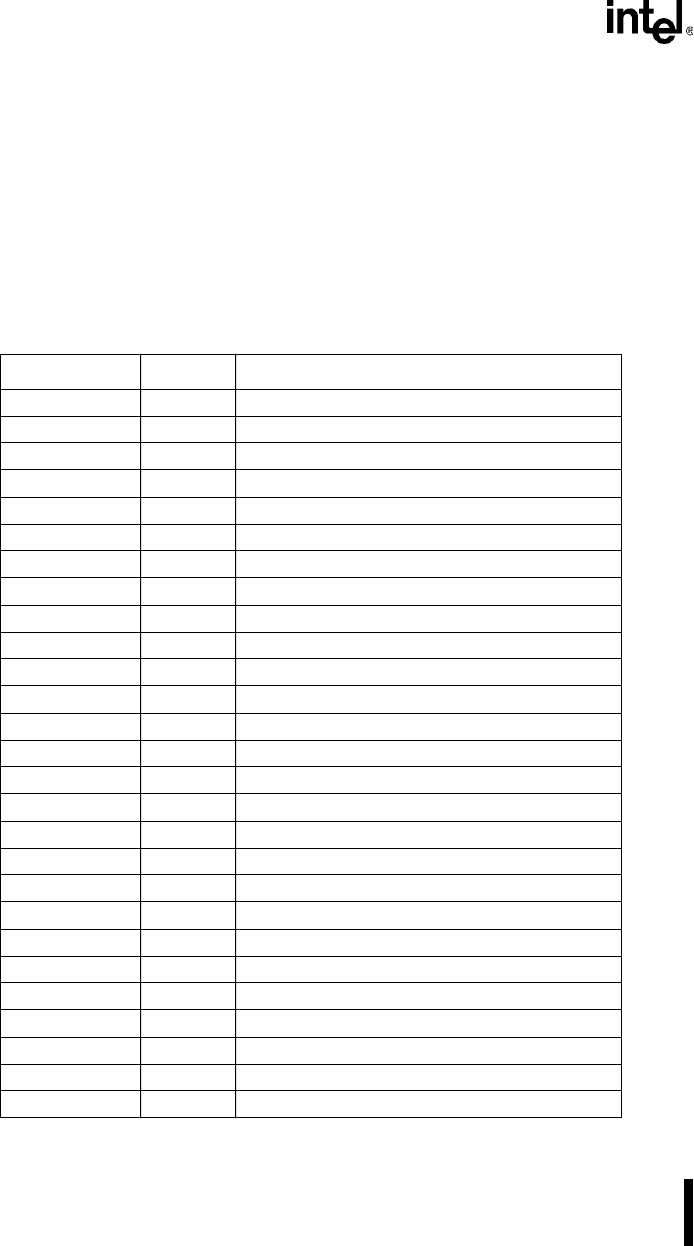

7.3.4.2 SMRAM State Dump Area

The SMM State Save sequence asserts SMIACT#. This mechanism indicates to internal modules

that the CPU has entered and is currently executing SMM. The resume (RSM) instruction is only

valid when in SMM. SMRAM space is an area located in the memory address range 38000H–

3FFFFH. The SMRAM area cannot be relocated internally. SMRAM space is intended for access

by the CPU only, and should be accessible only when SMM is enabled. This area is used by the

SMM State Save sequence to save the CPU state in a stack-like fashion from the top of the

SMRAM area downward.

The CPU state dump area always starts at 3FFFFH and ends at 3FE00H. The following is a map

of the CPU state dump in the SMRAM.

Hex Address Name Description

03FFFC CR0 Control flags that affect the processor state

03FFF8 CR3 Page directory base register

03FFF4 EFLGS General condition and control flags

03FFF0 EIP Instruction pointer

03FFEC EDI Destination index

03FFE8 ESI Source index

03FFE4 EBP Base pointer

03FFE0 ESP Stack pointer

03FFDC EBX General register

03FFC8 EDX General register

03FFD4 ECX General register

03FFD0 EAX General register

03FFCC DR6 Debug register; contains status at exception

03FFC8 DR7 Debug register; controls breakpoints

03FFC4 TR Task register; used to access current task descriptor

03FFC0 LDTR Local descriptor table pointer

03FFBC GS General-purpose segment register

03FFB8 FS General-purpose segment register

03FFB4 DS Data segment register

03FFB0 SS Stack segment register

03FFAC CS Code segment register

03FFA8 ES General-purpose segment register

03FFA7–03FF04 — Reserved

03FF02 — Halt restart slot

03FF00 — I/O trap restart slot

03FEFC — SMM revision identifier (10000H)

03FEFB–03FE00 — Reserved