2-3

ARCHITECTURAL OVERVIEW

2.2 INTEGRATED PERIPHERALS

The Intel386 EX processor integrates both PC-compatible peripherals (Table 2-1) and peripherals

that are specific to embedded applications (Table 2-2).

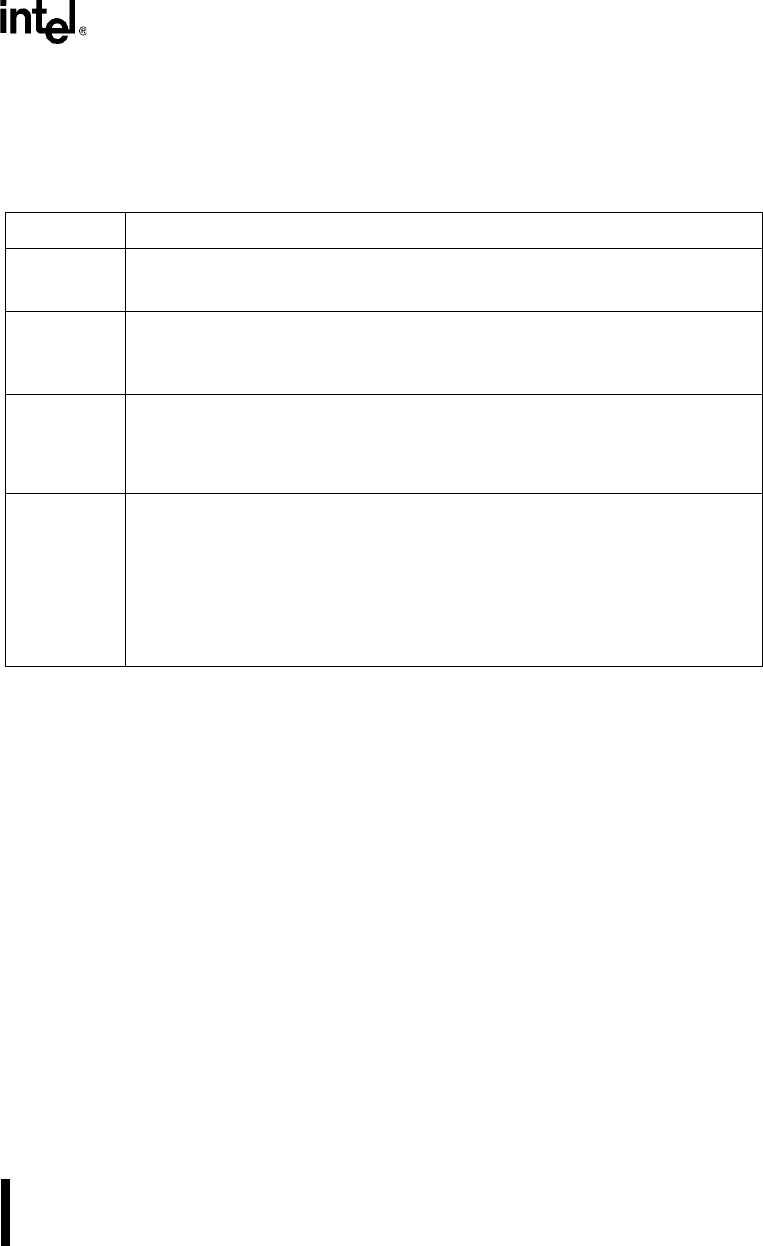

Table 2-1. PC-compatible Peripherals

Name Description

Interrupt

Control Unit

(ICU)

Consists of two 82C59A programmable interrupt controllers (PICs) configured as master

and slave. You may cascade up to six external 82C59A PICs to expand the external

interrupt lines to 52. Refer to Chapter 9, “INTERRUPT CONTROL UNIT.”

Timer/counter

Unit (TCU)

Provides three independent 16-bit down counters. The programmable TCU is

functionally equivalent to three 82C54 counter/timers with enhancements to allow

remapping of peripheral addresses and interrupt assignments. Refer to Chapter 10,

“TIMER/COUNTER UNIT.”

Asynchronous

Serial I/O

(SIO) Unit

Features two independent universal asynchronous receiver and transmitter (UART)

units which are functionally equivalent to National Semiconductor’s NS16450. Each

channel contains a baud-rate generator, transmitter, receiver, and modem control unit.

Receive and transmit interrupt signals can be connected to the ICU controller and DMA

controller. Refer to Chapter 11, “ASYNCHRONOUS SERIAL I/O UNIT.”

Direct Memory

Access

(DMA)

Controller

Transfers internal or external data between any combination of memory and I/O devices

for the entire 26-bit address bus. The two independent channels operate in 16- or 8-bit

bus mode. Buffer chaining allows data to be transferred into noncontiguous memory

buffers. The DMA channels can be tied to any of the serial devices to support high data

rates, minimizing processor interruptions. Provides a special two-cycle mode that uses

only one channel for memory-to-memory transfers. Bus arbitration logic resolves priority

conflicts between the DMA channels, the refresh control unit, and an external bus

master. SIO and SSIO interrupts can be connected to DMA for high-speed transfers.

Backward compatible with 8237A. Refer to Chapter 12, “DMA CONTROLLER.”