Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

13-4

13.1.1 SSIO Signals

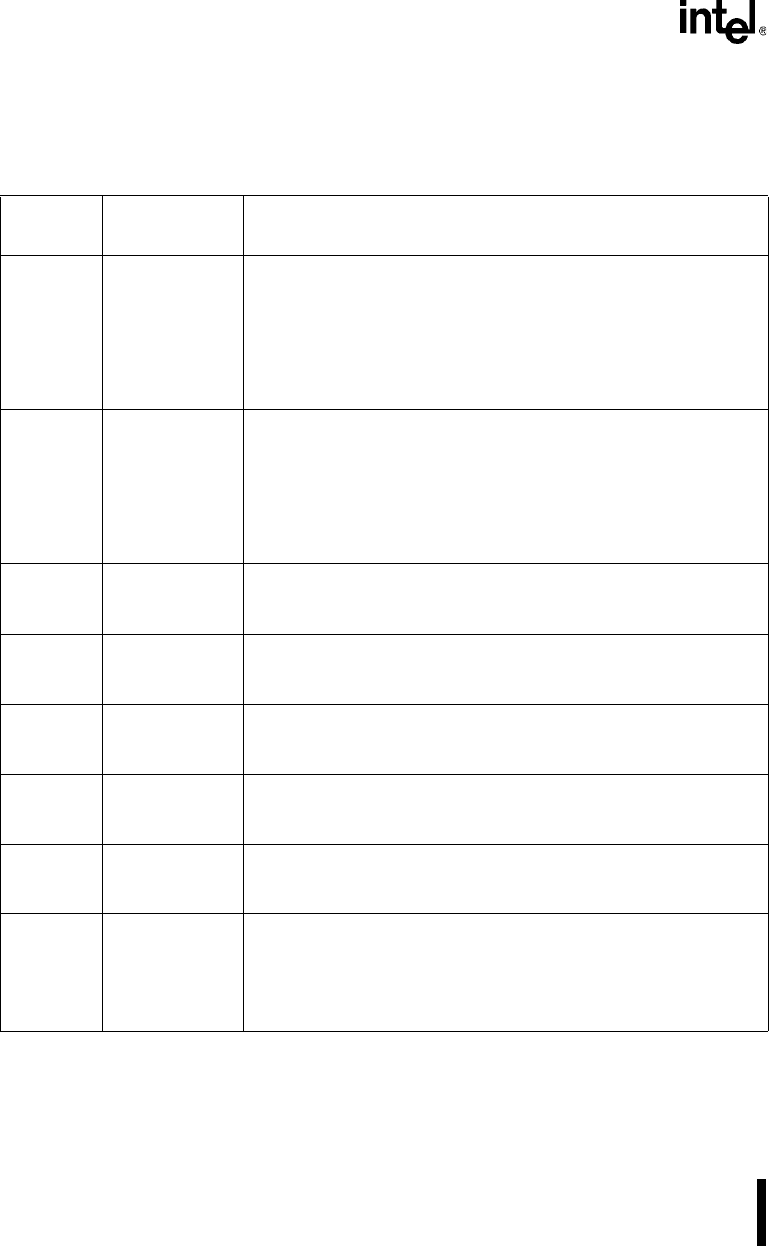

Table 13-1 lists the SSIO signals.

Table 13-1. SSIO Signals

Signal

Device Pin or

Internal Signal

Description

STXCLK Device pin

(input or output)

Serial Transmit Clock:

This pin functions as either an output or an input, depending on whether

the transmitter is operating in master or slave mode.

In master mode, STXCLK functions as an output. The baud-rate

generator’s output appears on this pin through the transmitter and can be

used to clock a slave receiver.

In slave mode, STXCLK functions as an input clock for the transmitter.

SRXCLK Device pin

(input or output)

Serial Receive Clock:

This pin functions as either an output or an input, depending on whether

the receiver is operating in master or slave mode.

In master mode, SRXCLK functions as an output. The baud-rate

generator’s output appears on this pin through the receiver and can be

used to clock a slave transmitter.

In slave mode, SRXCLK functions as an input clock for the receiver.

SSIOTX Device pin

(output)

Transmit Serial Data:

The transmitter uses this pin to shift serial data out of the device. Data is

transmitted most-significant bit first.

SSIORX Device pin

(input)

Receive Serial Data:

The receiver uses this pin to shift serial data into the device. Data is

received most-significant bit first.

SSRBF Internal signal

(output)

Receive Buffer Full:

This internal signal is used to indicate that received serial data has been

transferred from the receive shift register to the receive holding buffer.

SSTBE Internal signal

(output)

Transmit Buffer Empty:

This internal signal is used to indicate that serial data has been shifted

from the transmit holding register to the transmit shift register.

SSIOINT Internal signal

(output)

SSIO Interrupt:

This internal signal goes active when either the transmit holding register

is empty or the receive holding register is full.

BCLKIN Internal signal

(input)

Prescaled Clock (PSCLK)

:

This internal signal is a prescaled value of the internal clock frequency

(CLK2/2). PSCLK is programmable for a range of divide-by values.

Serial Clock (SERCLK)

:

This internal signal is half the internal clock frequency (CLK2/4).