9-17

INTERRUPT CONTROL UNIT

To initialize the 82C59As:

1. Globally disable all maskable interrupts to the core using the CLI instruction.

2. Write to the initialization command words.

NOTE

You must initialize both the master and the slave (either can be initialized

first).

The 8259A module has a state machine that controls access to the individual registers. Improper

initialization occurs when the following sequences are not followed:

• To initialize the master, write to its initialization command words in order (ICW1, ICW2,

ICW3, then ICW4).

• To initialize the slave, write to its initialization command words in order (ICW1, ICW2,

ICW3, then ICW4).

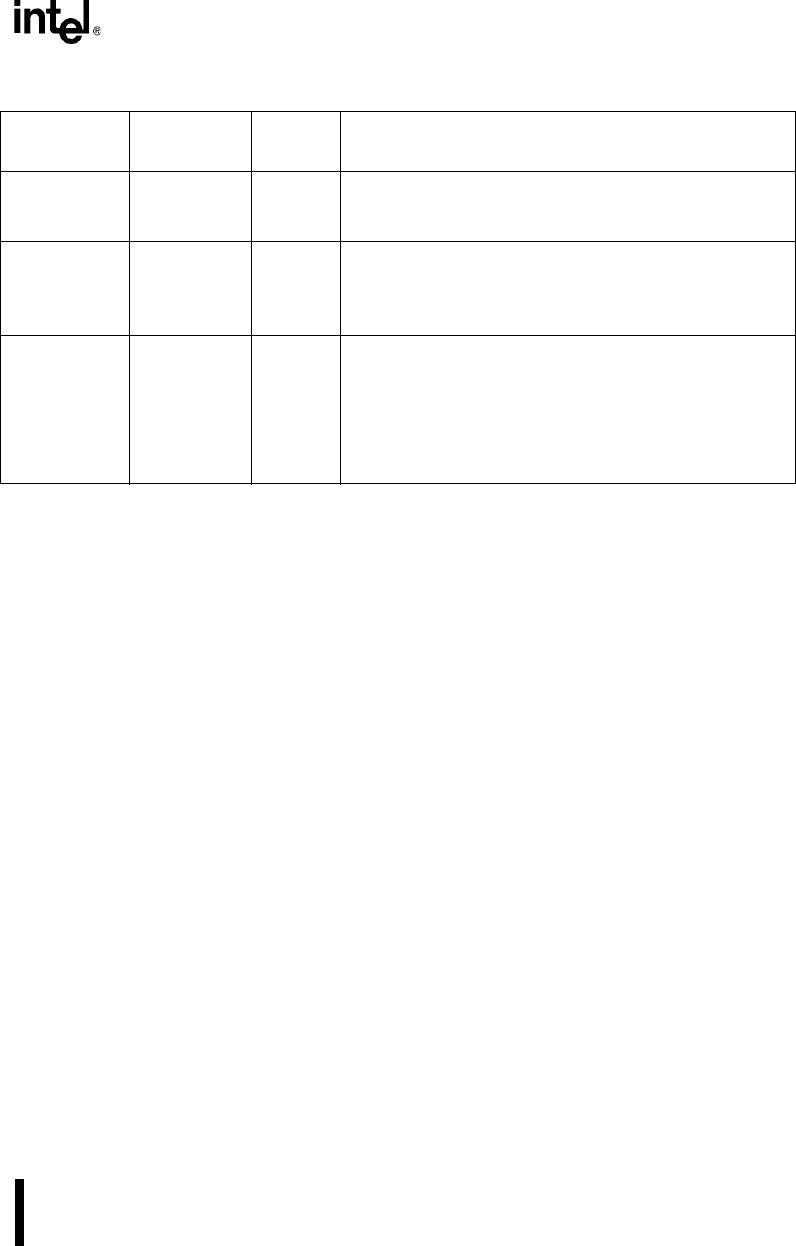

IRR (master)

IRR (slave)

(read only)

0F020H

0F0A0H

0020H

00A0H

Interrupt Request:

Indicates pending interrupt requests.

ISR (master)

ISR (slave)

(read only)

0F020H

0F0A0H

0020H

00A0H

In-service:

Indicates the interrupt requests that are currently being

serviced.

POLL (master)

POLL (slave)

(read only)

0F020H

0F021H

0F0A0H

0F0A1H

0020H

0021H

00A0H

00A1H

Poll Status Byte:

Indicates whether any of the devices connected to the 82C59A

require servicing. If the 82C59A requires servicing, this byte

indicates the highest-priority pending interrupt.

NOTE: Once the polling bit is set in OCW3, the Poll Status

Byte of a particular 82C59A can be read by doing an access to

any of the four addresses of that 82C59A.

Table 9-2. ICU Registers (Sheet 2 of 2)

Register

Expanded

Address

PC/AT*

Address

Function

NOTE: All master 82C59A registers are accessed through two expanded or PC/AT addresses; all the slave

registers are accessed through two other expanded or PC/AT addresses. The order in which you write

or read these addresses along with certain register bit settings determines which register is accessed.