5-9

DEVICE CONFIGURATION

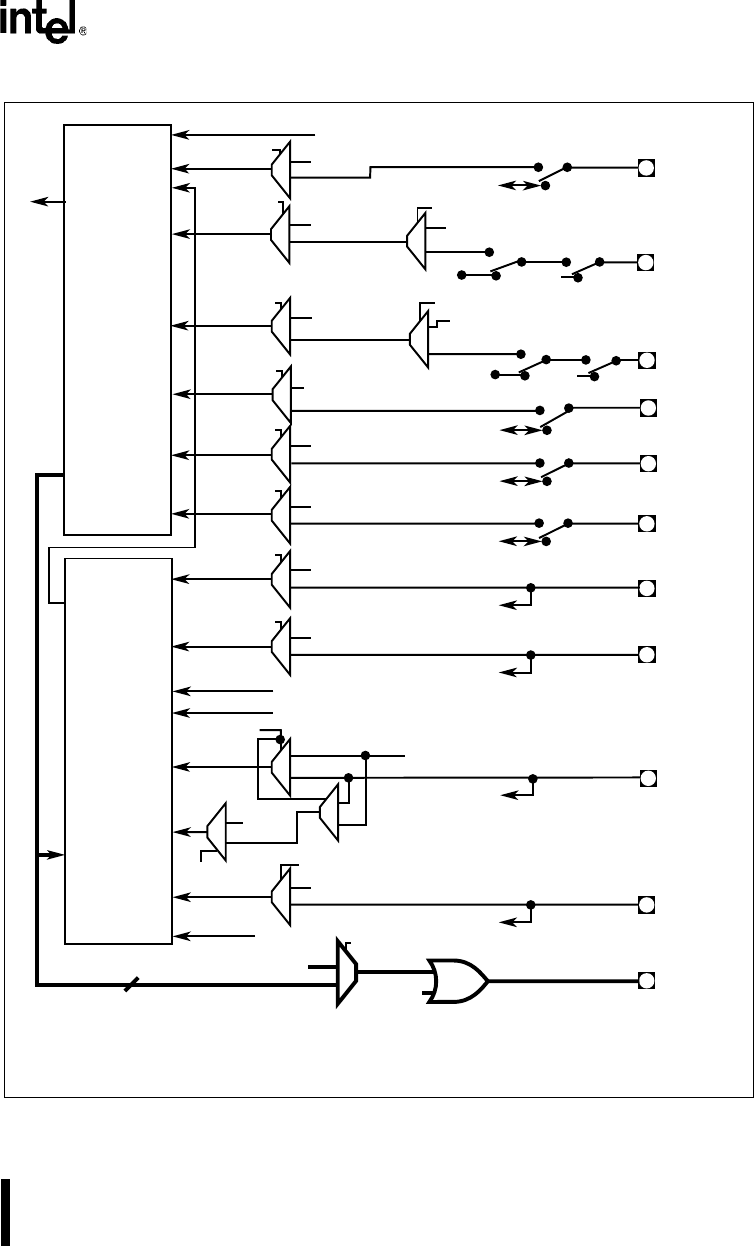

Figure 5-4. Interrupt Control Unit Configuration

IR0

IR1

IR2

8259A

Master

IR4

0

1

INT0

(P3.2)†

To/From I/O Port 3

P3CFG.2

V

SS

P3CFG.2

IR5

IR6

IR7

OUT0 (TCU)

IR3

SIOINT0

INT1

(P3.3)

To/From I/O Port 3

P3CFG.3

V

SS

P3CFG.3

INT2

(P3.4)

To/From I/O Port 3

P3CFG.4

V

SS

P3CFG.4

INT3

(P3.5)

To/From I/O Port 3

P3CFG.5

V

SS

P3CFG.5

IR0

IR1

IR2

IR4

IR5

IR6

IR3

INT4

V

SS

INTCFG.0

INT5

To TCU

SSIOINT

INTCFG.1

INT6

To TCU

V

SS

INTCFG.2

OUT1(TCU)

OUT2(TCU)

DMAINT

INT7

To TCU

V

SS

INTCFG.3

0

1

CAS2:0

(A18:16)

V

SS

A18:16

INTCFG.7

8259A

Slave

INT

CAS2:0

CAS2:0

3

A2522-03

IR7

WDTOUT#

To TCU

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

INTCFG.4

0

1

0

1

INTCFG.5

MCR0.3

SIOINT0

INT9

TMROUT0

(P3.0)

OUT0(TCU)

INTCFG.5

SIOINT1

0

1

0

1

INTCFG.6

MCR1.3

SIOINT1

INT8

TMROUT1

(P3.1)

OUT1(TCU)

INTCFG.6

† Alternate pin signals are in parentheses

Heavier lines indicate multiple signals.

INT

INTR

(to

core)

1

1

0

0

1

P3CFG.1

P3.1

1

0

(TMRGATE0)

(TMRCLK0)

0

1

P3.0

P3GFG.0

0

1

0

1

(TMRGATE1)

(TMRCLK1)

0

0

1