Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

14-14

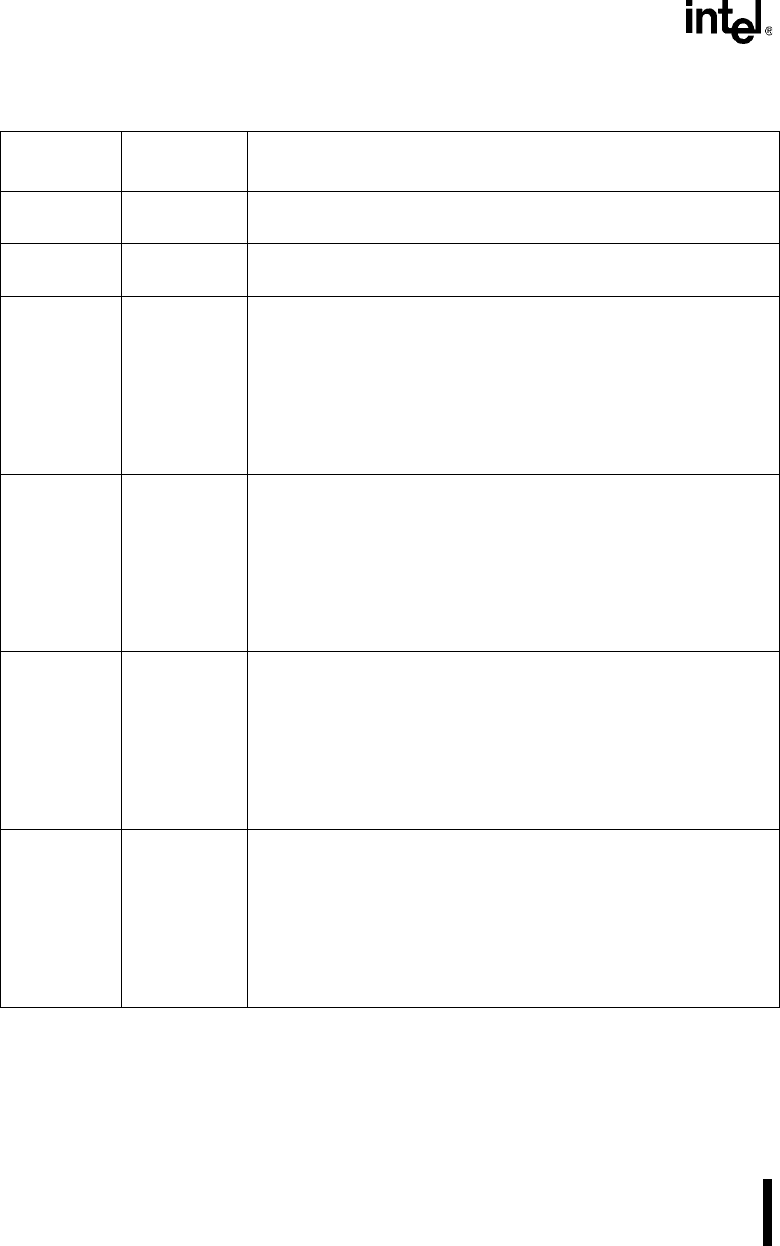

Table 14-2. CSU Registers

Register

Expanded

Address

Description

PINCFG

(read/write)

0F826H Pin Configuration:

Connects the CS6:5# signals to package pins.

P2CFG

(read/write)

0F822H Port 2 Configuration:

Connects the CS4:0# signals to package pins.

CS0ADH

CS1ADH

CS2ADH

CS3ADH

CS4ADH

CS5ADH

CS6ADH

UCSADH

(read/write)

0F402H

0F40AH

0F412H

0F41AH

0F422H

0F42AH

0F432H

0F43AH

Chip-select High Address:

Defines the upper 10 bits of the chip-select channel address. The

processor uses a chip-select’s channel address to determine the starting

location of the channel’s active address block.

CS0ADL

CS1ADL

CS2ADL

CS3ADL

CS4ADL

CS5ADL

CS6ADL

UCSADL

(read/write)

0F400H

0F408H

0F410H

0F418H

0F420H

0F428H

0F430H

0F438H

Chip-select Low Address:

Defines the lower 5 bits of the chip-select channel address. Configures

the channel for memory or I/O addresses, determines whether or not the

channel is activated when the processor is operating in system

management mode, configures the channel’s bus size, defines the

minimum number of wait states inserted into the bus cycle, and defines

whether an external READY# is required to terminate the bus cycle.

CS0MSKH

CS1MSKH

CS2MSKH

CS3MSKH

CS4MSKH

CS5MSKH

CS6MSKH

UCSMSKH

(read/write)

0F406H

0F40EH

0F416H

0F41EH

0F426H

0F42EH

0F436H

0F43EH

Chip-select High Mask:

Defines the upper 10 bits of the chip-select channel mask. The processor

uses a chip-select’s channel mask to determine the size of the channel’s

active address block and if the address block is repeated.

CS0MSKL

CS1MSKL

CS2MSKL

CS3MSKL

CS4MSKL

CS5MSKL

CS6MSKL

UCSMSKL

(read/write)

0F404H

0F40CH

0F414H

0F41CH

0F424H

0F42CH

0F434H

0F43CH

Chip-select Low Mask:

Defines the lower 5 bits of the chip-select channel mask and enables the

channel’s output pin.