Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

15-10

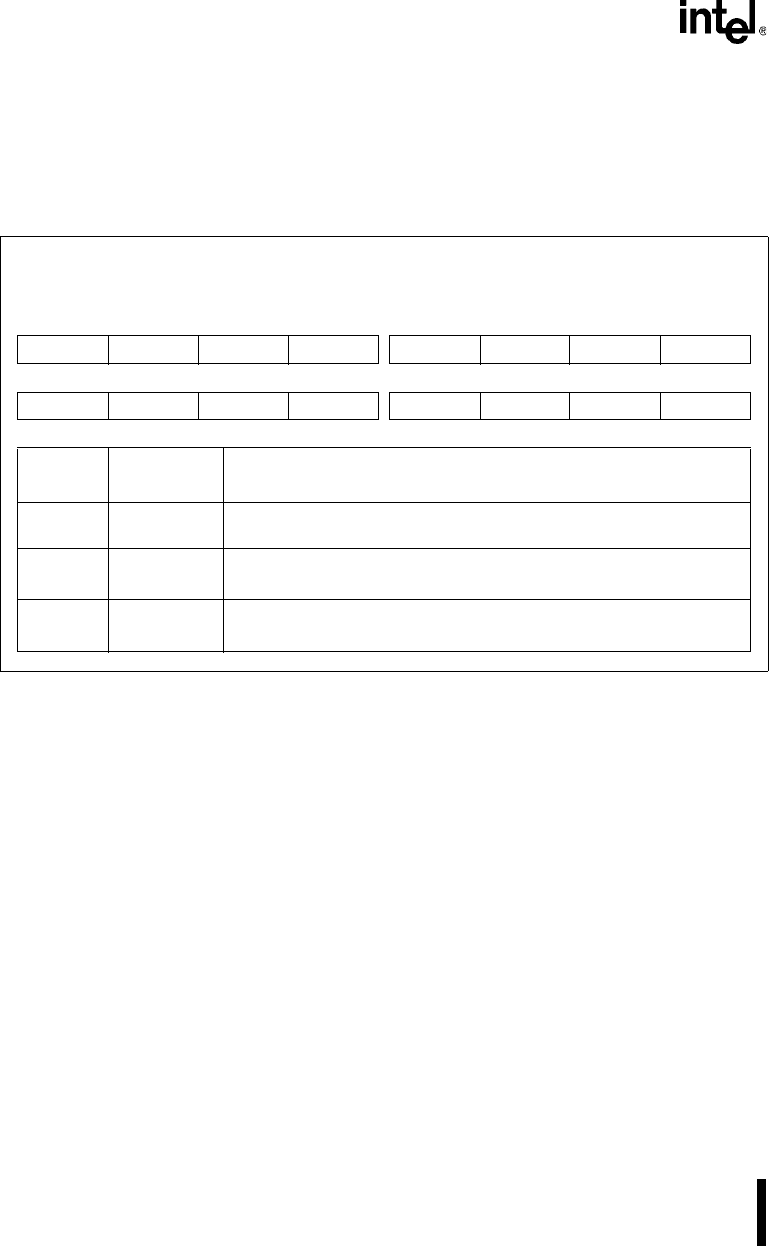

15.4.4 Refresh Address Register (RFSADD)

RFSADD contains the bits A13:1 of the refresh address. The lowest address bit is not used be-

cause most DRAM devices contain word-wide memory arrays; for all refresh operations, the low-

est address bit remains set.

Figure 15-5. Refresh Address Register (RFSADD)

Refresh Address

RFSADD

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F4A6H

—

00FFH

15 8

— — RA13 RA12 RA11 RA10 RA9 RA8

7 0

RA7 RA6 RA5 RA4 RA3 RA2 RA1 1

Bit

Number

Bit

Mnemonic

Function

15–14 — Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

13–1 RA13:1 Refresh Address Bits:

These bits comprise A13:1 of the refresh address.

0 — Refresh Bit 0:

A0 of the refresh address. This bit is always 1 and is read-only.