18-7

JTAG TEST-LOGIC UNIT

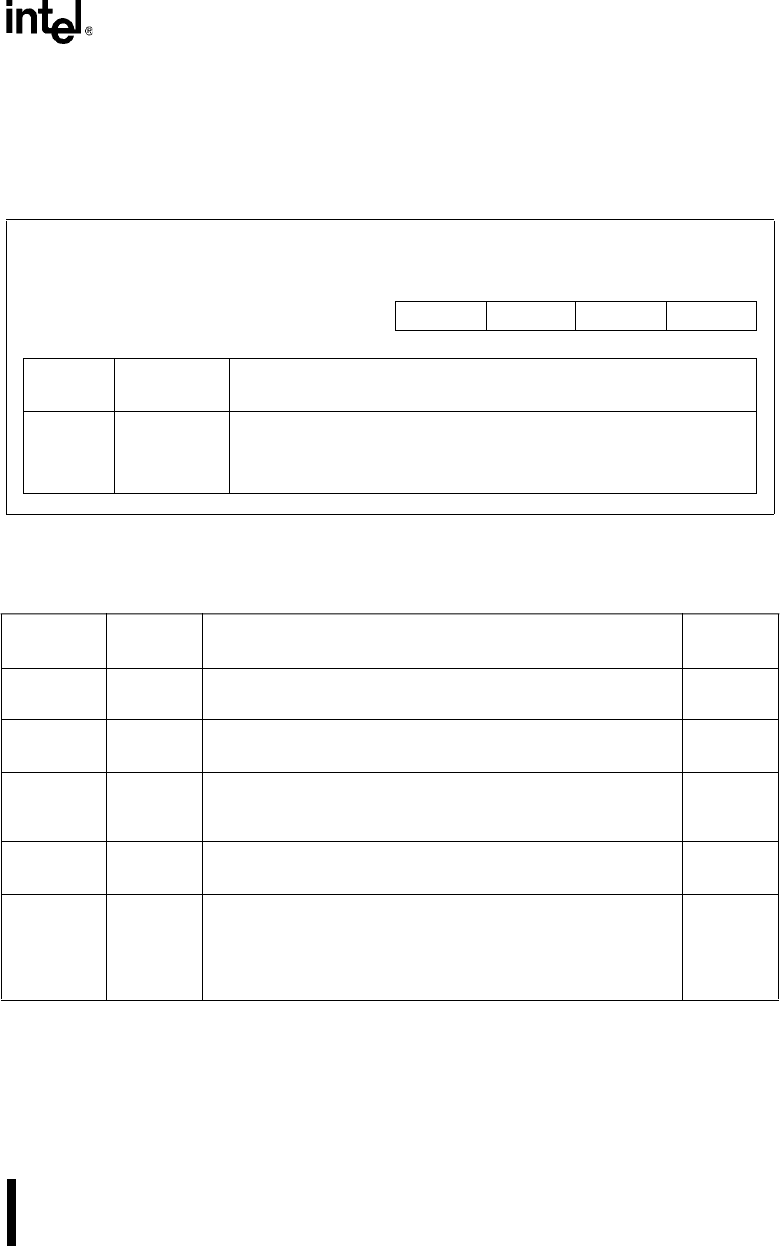

18.2.3 Instruction Register (IR)

An instruction opcode is clocked serially through the TDI pin into the four-bit instruction register

(Figure 18-3). The instruction determines which data register is affected. Table 18-4 lists the in-

structions with their binary opcodes, descriptions, and associated registers.

Figure 18-3. Instruction Register (IR)

Instruction Register

IR

Reset State

(Using TRST#): 02H

3 0

INST3 INST2 INST1 INST0

Bit

Number

Bit

Mnemonic

Function

3–0 INST3:0 Instruction opcode. At reset (using TRST#, or after 5 TCK cycles with

TMS held low), this field is loaded with 0010, the opcode for the IDCODE

instruction. Instructions are shifted into this field serially through the TDI

pin. (Table 18-4 lists the valid instruction opcodes.)

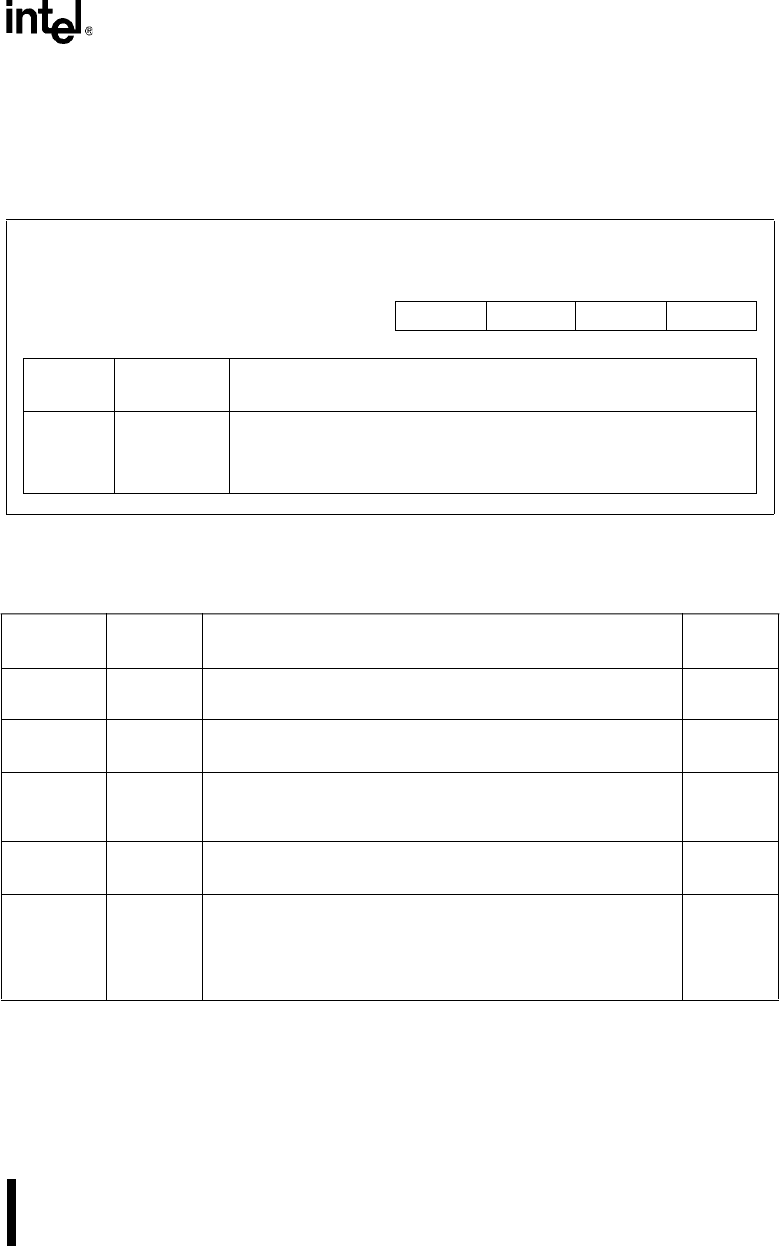

Table 18-4. Test-logic Unit Instructions

Mnemonic Opcode† Description

Affected

Register

BYPASS

1111 Bypass on-chip system logic (mandatory instruction).

Used for those components that are not being tested.

BYPASS

EXTEST

0000 Off-chip circuitry test (mandatory instruction).

Used for testing device interconnections on a board.

BOUND

SAMPRE

0001 Sample pins/preload data (mandatory instruction).

Used for controlling (preload) or observing (sample) the signals at

device pins. This test has no effect on system operation.

BOUND

IDCODE

0010 ID code test (optional instruction).

Used to identify devices on a board.

IDCODE

HIGHZ

1000 High-impedance/On-Circuit Emulation (ONCE) mode test

(optional instruction).

Used to place device pins into their inactive drive states. Allows

external components to drive signals onto connections that the

processor normally drives.

BYPASS

†

The opcode is the sequence of data bits shifted serially into the instruction register (IR) from the TDI input.

The opcodes for EXTEST and BYPASS are mandated by IEEE 1149.1, so they should be the same for all

JTAG-compliant devices. The remaining opcodes are designer-defined, so they may vary among devices.

All unlisted opcodes are reserved. Use of reserved opcodes could cause the device to enter reserved

factory-test modes.