7-3

SYSTEM MANAGEMENT MODE

ports the relocation of SMRAM. When this bit is set (1), the processor supports SMRAM reloca-

tion. When this bit is cleared (0), then the processor does not support SMRAM relocation. Since

this device doesn’t support SMRAM relocation, bit 17 of the SMM Revision Identifier is cleared.

The SMRAM address space is fixed from 38000H to 3FFFFH.

7.3 SYSTEM MANAGEMENT MODE PROGRAMMING AND CONFIGURATION

7.3.1 Register Status During SMM

When the CPU recognizes SMI# on an instruction boundary, it waits for all write cycles to com-

plete and asserts the SMIACT# pin. The processor then saves its register state to SMRAM space

and begins to execute the SMM handler. The RSM instruction restores the registers, deasserts the

SMIACT# pin, and returns to the user program.

Upon entering SMM, the processor’s PE, MP, EM, TS and PG bits in CR0 are cleared, as shown

in Table 7-1.

Debug register DR7 is also cleared, except for bits 11–15.

Internally, a descriptor register (invisible to the programmer) is associated with each program-

mer-visible segment register. Each descriptor register holds a 32-bit segment base address, a 32-

bit segment limit, and other necessary segment attributes. When a selector value is loaded into a

segment register, the associated descriptor register is automatically updated with the correct in-

formation. In Real mode, only the base address is updated directly (by shifting the selector value

four bits to the left), since the segment maximum limit and attributes are fixed in Real mode. In

Protected mode, the base address, the limit, and the attributes are all updated per the contents of

the segment descriptor indexed by the selector. After saving the CPU state, the SMM State Save

sequence sets the appropriate bits in the segment descriptor, placing the core in an environment

similar to Real mode, without the 64 Kbyte limit checking.

In SMM, the CPU executes in a Real-like mode. In this mode, the CPU can access (read and

write) any location within the 4 Gbyte logical address space. The physical address space is

64 Mbytes. The CPU can also perform a jump and a call anywhere within a 1 Mbyte boundary

address space. In SMM, the processor generates addresses as it does in real mode; however, there

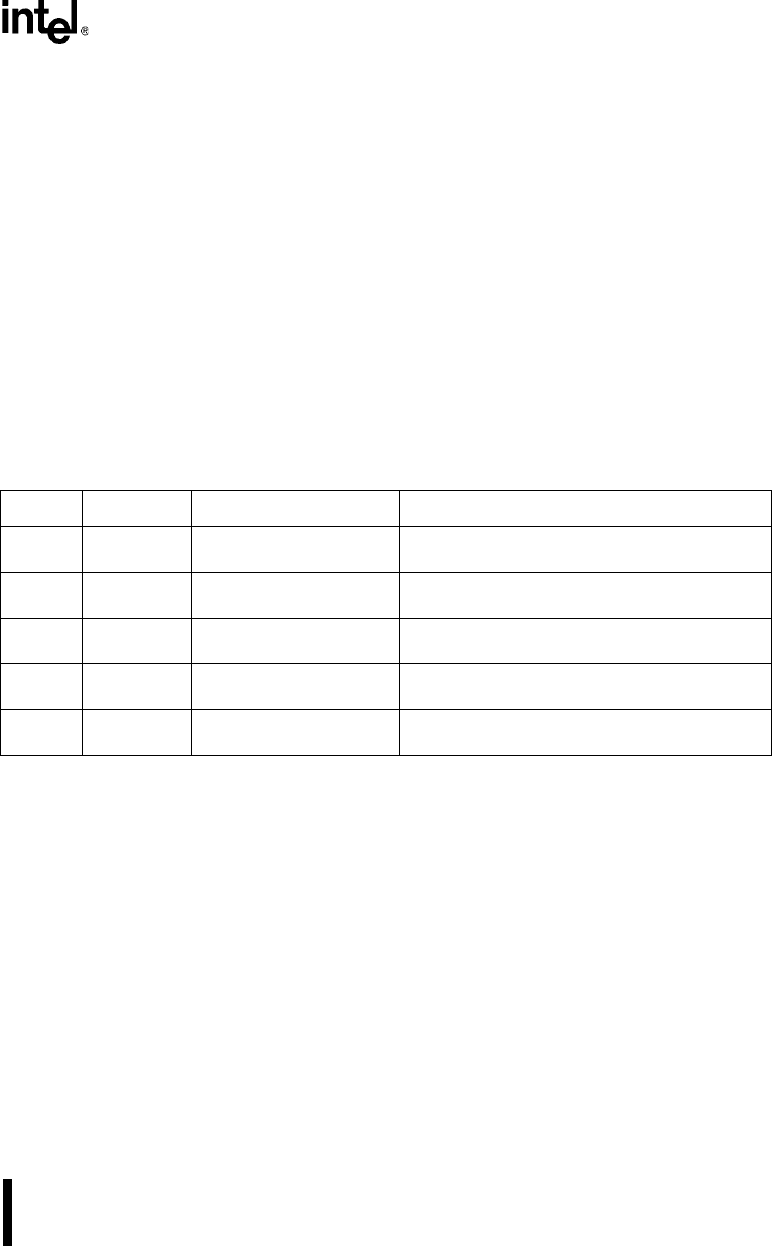

Table 7-1. CR0 Bits Cleared Upon Entering SMM

CR0 Bit Mnemonic Description Function

0 PE Protection Enable 0 = protection disabled

1 = protection enabled

1 MP Math Coprocessor Present 0 = coprocessor not present

1 = coprocessor present

2 EM Emulate Coprocessor 0 = coprocessor opcodes execute

1 = coprocessor opcodes generate a fault

3 TS Task Switched 0 = coprocessor ESC opcode does not cause fault

1 = coprocessor ESC opcode causes fault

31 PG Paging Enable 0 = paging disabled

1 = paging enabled