D-37

SYSTEM REGISTER QUICK REFERENCE

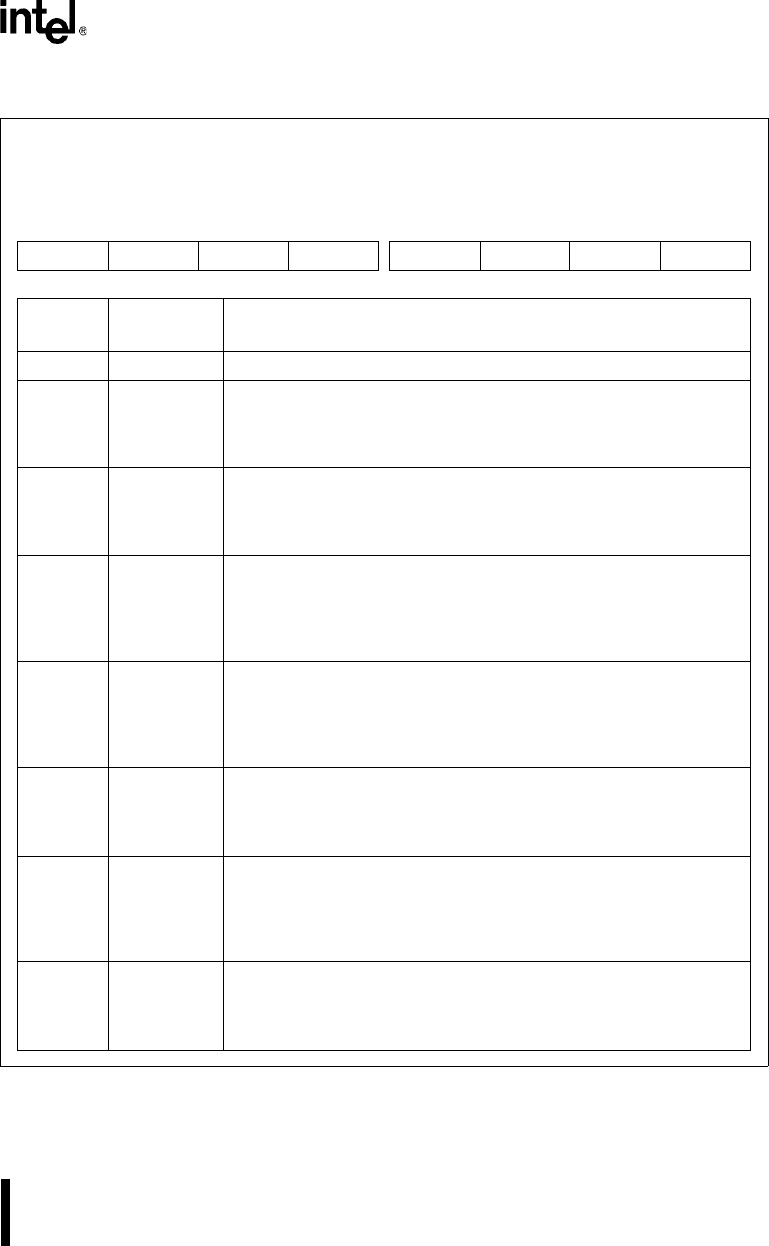

D.34 LSR

n

Serial Line Status

LSR0, LSR1

(read only)

Expanded Addr:

ISA Addr:

Reset State:

LSR0 LSR1

F4FDH F8FDH

03FDH 02FDH

60H 60H

7 0

— TE TBE BI FE PE OE RBF

Bit

Number

Bit

Mnemonic

Function

7 — Reserved. This bit is undefined.

6 TE Transmitter Empty:

The transmitter sets this bit to indicate that the transmit shift register and

transmit buffer register are both empty. Writing to the transmit buffer

register clears this bit.

5 TBE Transmit Buffer Empty:

The transmitter sets this bit after it transfers data from the transmit buffer

to the transmit shift register. Writing to the transmit buffer register clears

this bit.

4 BI Break Interrupt:

The receiver sets this bit whenever the received data input is held in the

spacing (logic 0) state for longer than a full word transmission time.

Reading the receive buffer register or the serial line status register clears

this bit.

3 FE Framing Error

The receiver sets this bit to indicate that the received character did not

have a valid stop bit. Reading the receive buffer register or the serial line

status register clears this bit. If data frame is set for two stop bits the

second stop bit is ignored.

2 PE Parity Error:

The receiver sets this bit to indicate that the received data character did

not have the correct parity. Reading the receive buffer register or the

serial line status register clears this bit.

1 OE Overrun Error:

The receiver sets this bit to indicate an overrun error. An overrun occurs

when the receiver transfers a received character to the receive buffer

register before the CPU reads the buffer’s old character. Reading the

serial line status register clears this bit.

0 RBF Receive Buffer Full:

The receiver sets this bit after it transfers a received character from the

receive shift register to the receive buffer register. Reading the receive

buffer register clears this bit.