Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

E-2

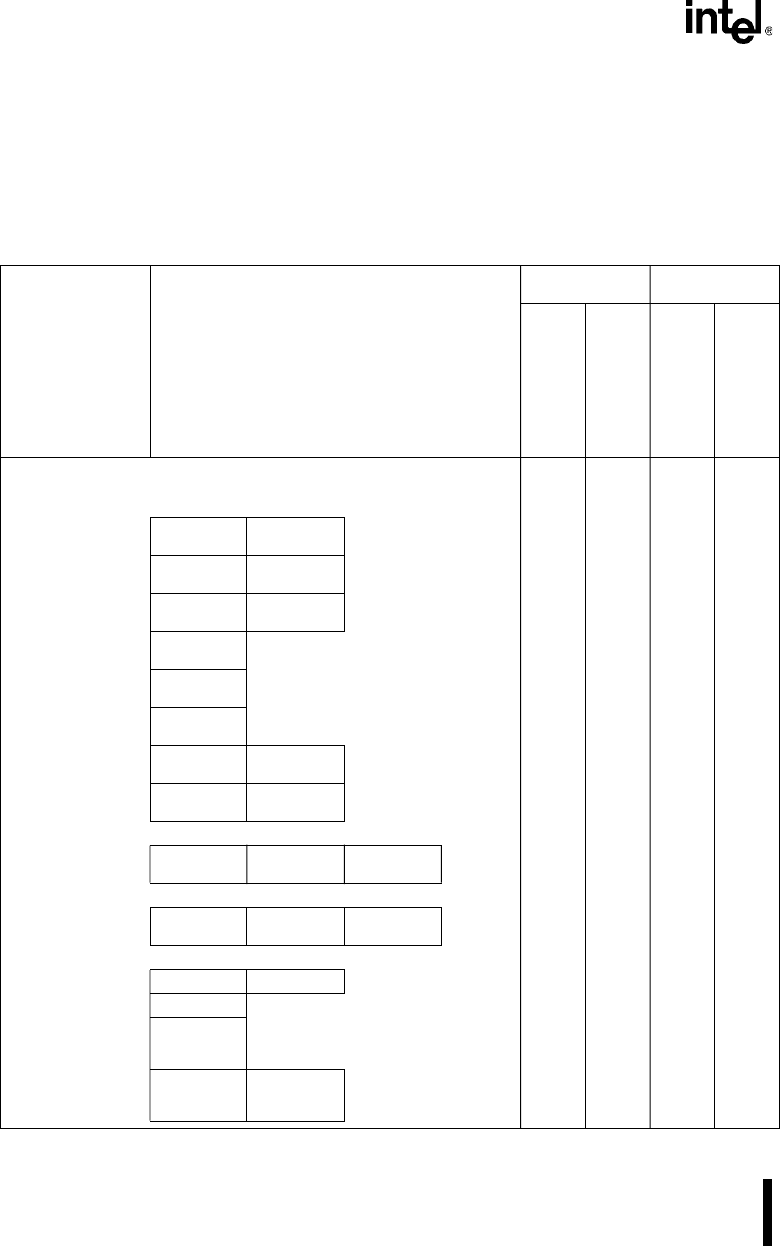

Wait states:

Wait states add 1 clock per wait state to instruction execution for each data access.

Table E-1 lists the instructions with their formats and execution times. The description of the

notes for Table E-1 begins on page E-20. See “Instruction Encoding” on page E-22 for the defi-

nition of the terms used in this table.

Table E-1. Instruction Set Summary (Sheet 1 of 19)

Instruction Format

Clock Count Notes

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode

GENERAL DATA TRANSFER

MOV = Move

register to

register/memory

1 0 0 0 1 0 0 w mod reg r/m

2/2 2/2* b h

register/memory to

register

1 0 0 0 1 0 1 w mod reg r/m

2/4 2/4* b h

immediate to

register/memory

1 1 0 0 0 1 1 w mod 0 0 0 r/m immediate data

2/2 2/2* b h

immediate to register

(short form)

1 0 1 1 w reg immediate data

22

memory to accumulator

(short form)

1 0 1 0 0 0 0 w full displacement

4* 4* b h

accumulator to memory

(short form)

1 0 1 0 0 0 1 w full displacement

2* 2* b h

register memory to

segment register

1 0 0 0 1 1 1 0 mod sreg3 r/m

2/5 22/23 b h, i, j

segment register to

register/memory

1 0 0 0 1 1 0 0 mod sreg3 r/m

2/2 2/2 b h

MOVSX = Move with sign extension

register from

register/memory

0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 w mod reg r/m

3/6* 3/6* b h

MOVZX = Move with zero extension

register from

register/memory

0 0 0 0 1 1 1 1 1 0 1 1 0 1 1 w mod reg r/m

3/6* 3/6* b h

PUSH = Push

register/memory 1 1 1 1 1 1 1 1 mod 1 1 0 r/m 5/7* 7/9* b h

register (short form) 0 1 0 1 0 reg 24bh

segment register (ES,

CS, SS, or DS)

(short form)

000 sreg2 110

24bh

segment register (ES,

CS, SS, or DS, FS or

GS)

0 0 0 0 1 1 1 1 10 sreg3 000

24bh